# The Return of Silicon Efficiency

Simon Knowles Icera

#### **AGENDA**

- Chip Market

- Design Objectives

- Modern Transistors

- Optimality of Designs

- The Design Hull

- Implications for Design

## "The Cheap will Outsell the Good"

## **Customer Priorities**

- 1. Availability

- 2. Price

**Features**

3. Power Size

## **Design Choices**

- 1. Hardware ↔ Software

- 2. Process Technology

- 3. MHz and Volts

- 4. Custom ↔ Synthesized

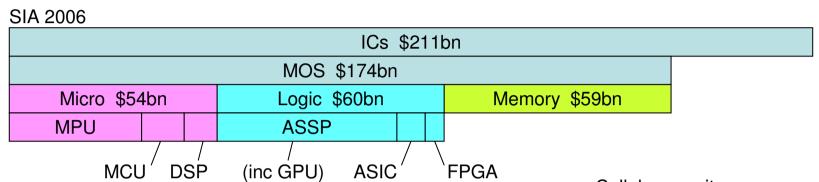

## The Chip Market

Most logic chips are processors or processor-centric.

Computers have driven MOS chip evolution – the first "product superclass".

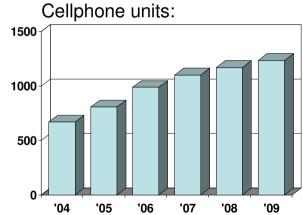

The second product superclass will be "cellphones"...

- Consumer driven more cost sensitive than computers.

- High mobility more power sensitive than computers.

- High (specialized) performance eg. HSDPA cellular modem ~50GOPs.

ICERA

## What's New(-ish) in Logic Chip Physics?

Small dopant populations (V<sub>T</sub> variability)

Subthreshold leakage (V<sub>T</sub> reduction is constrained, so Vdd likewise)

Gate leakage (end of SiO<sub>2</sub> T<sub>ox</sub> scaling)

Channel Stress (engineered and STI-induced)

**OPC** rules

Well Proximity Effect

Line Edge Roughness (gate and wire)

NBTI (RAM V<sub>T</sub> drift)

All important for designers, but not (directly) the main influencers of design evolution

### Top 2 Design Influencers

#### 1. Most power-sensitive designs will set their own supply voltage.

- Design at typical, turn manufacturing speed spread (functionality risk) into power efficiency spread (battery life).

- Offset manufacturing leakage spread against speed spread.

- Dynamically trade performance vs power.

- Disconnect power in standby (efficient regulators are switch-mode).

#### 2. Processors are evolving to displace fixed-function hardware

- Target multiple market sockets per design.

- Hardware-efficient (dynamic re-purposing of resources).

- Mitigation of specification uncertainty.

- Work around bugs by software change.

- Well-practiced idiom for speed.

ICERA

# **Modern Transistors**

### **Modern Transistors**

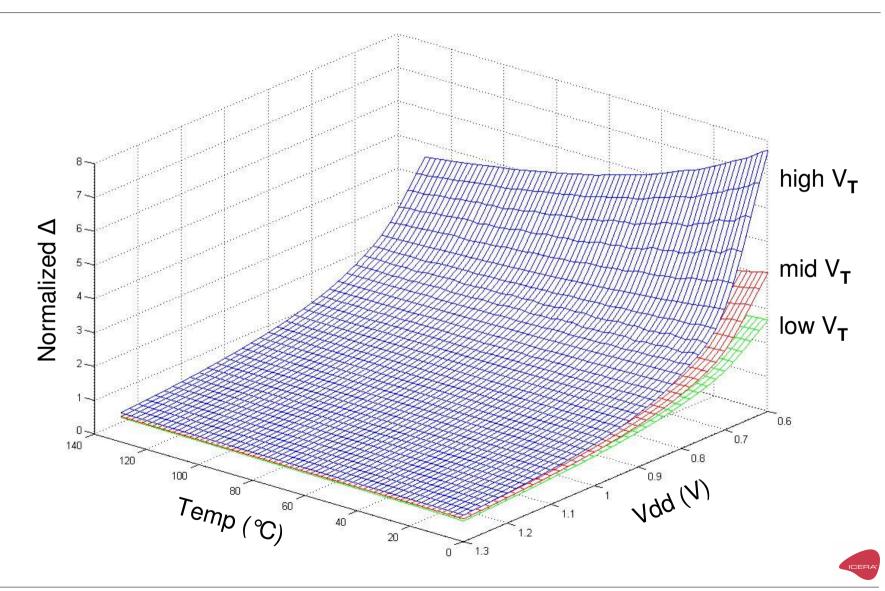

ITRS distinguishes 3 roadmaps...

- High Performance (HP)

- Low Operating Power (LOP)

- Low Standby Power (LSTP)

TSMC offers 12 logic T's at 65nm...

- 2 x HP

- 6 x LOP

- 4 x LSTP

#### ITRS2005 for 65nm 2007

|                                |      | L <sub>g</sub> (nm) | T <sub>ox</sub> (nm) | V <sub>T</sub> (mV) |

|--------------------------------|------|---------------------|----------------------|---------------------|

| computers $\left\{  ight.$     | HP   | 25                  | 1.1                  | 165                 |

| "cellphones" $\left\{ \right.$ | LOP  | 32                  | 1.2                  | 285                 |

|                                | LSTP | 45                  | 1.9                  | 524                 |

# 65nm LOP Delay

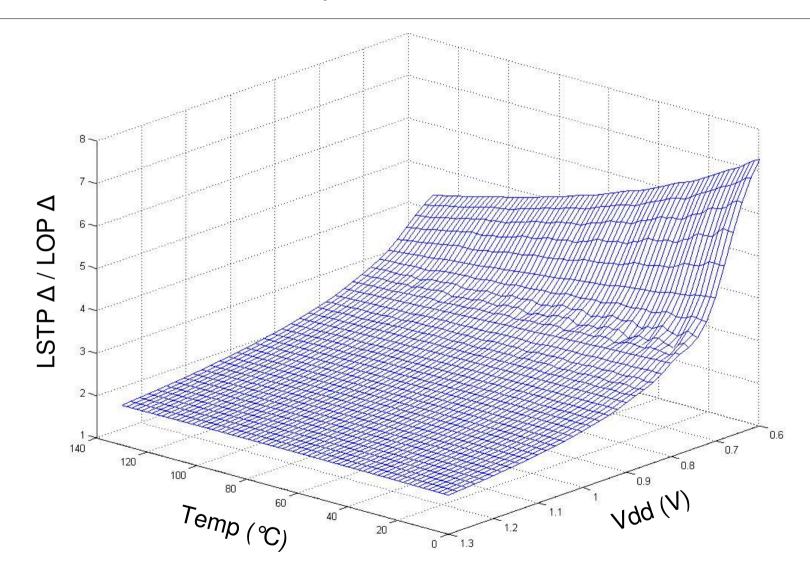

# 65nm LSTP vs LOP Delay

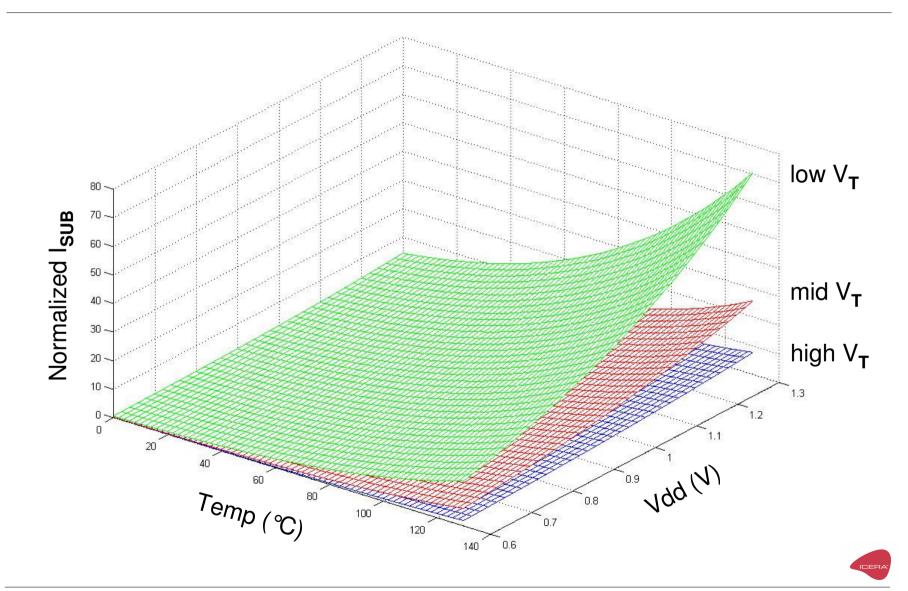

## 65nm LOP Sub-Threshold Leakage

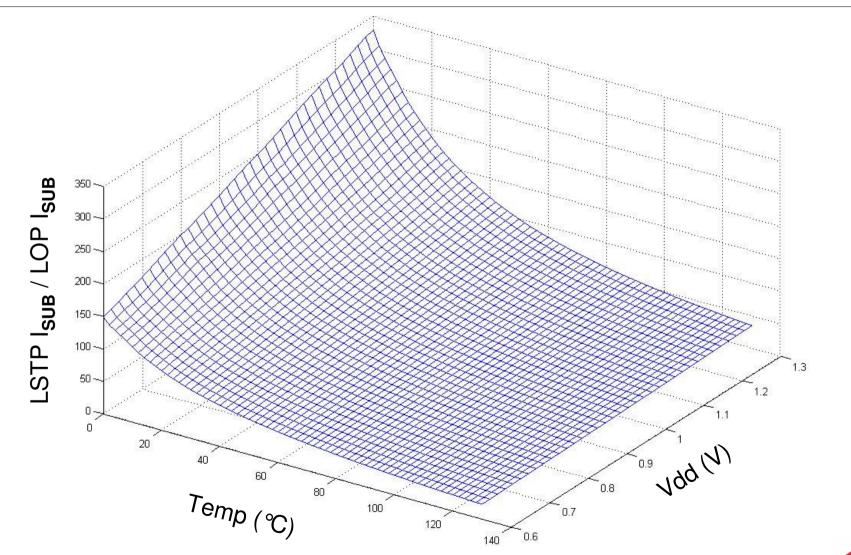

## 65nm LSTP vs LOP Sub-Threshold Leakage

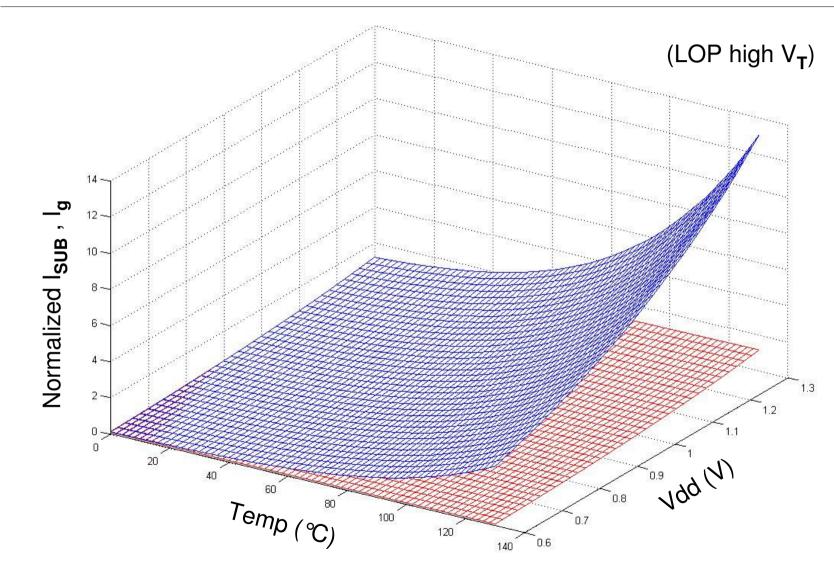

# High Temp $I_{SUB}$ Still Dominates $I_g$ at 65nm (LOP and LSTP)

ICERA"

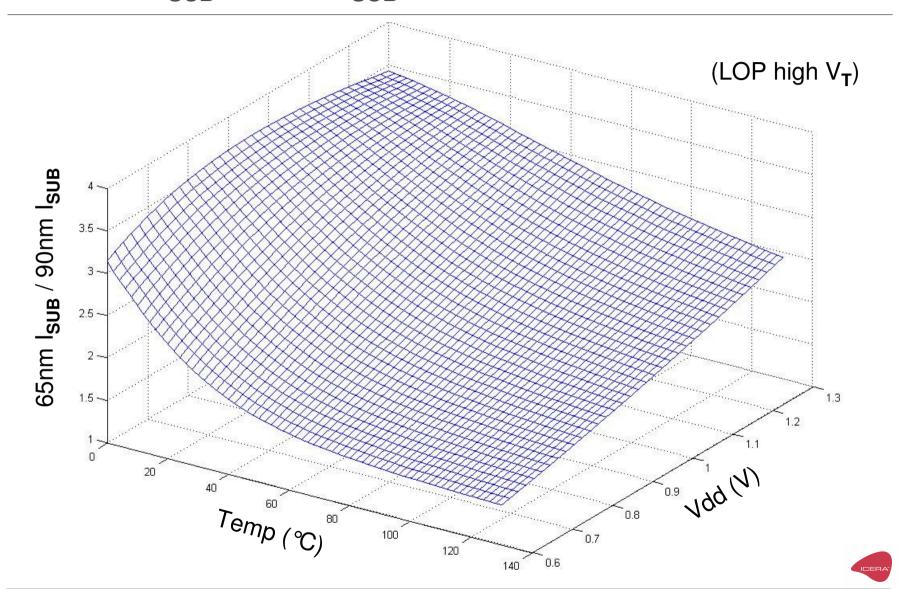

# $\mathsf{LOP}\ \mathsf{65nm}\ \mathsf{I}_{\mathbf{SUB}}\ \mathsf{vs}\ \mathsf{90nm}\ \mathsf{I}_{\mathbf{SUB}}$

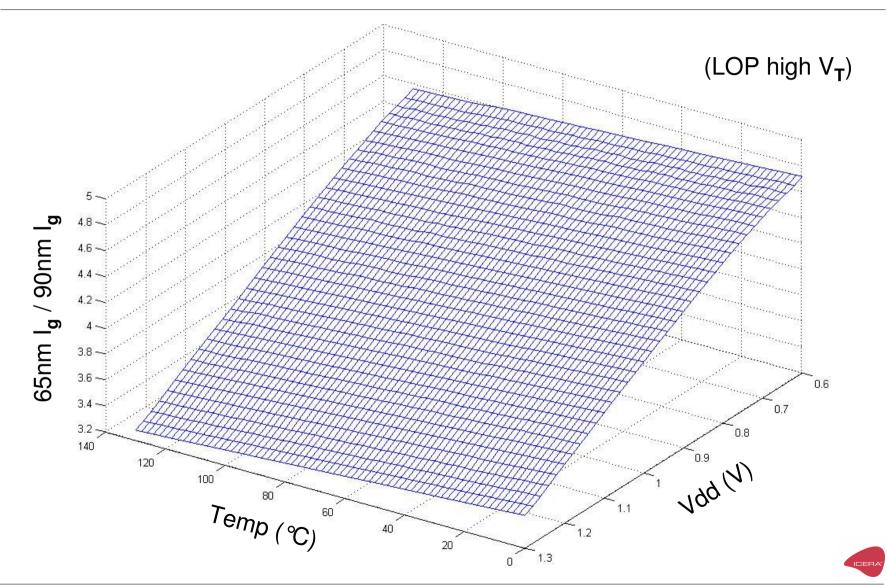

# $LOP 65nm I_g vs 90nm I_g$

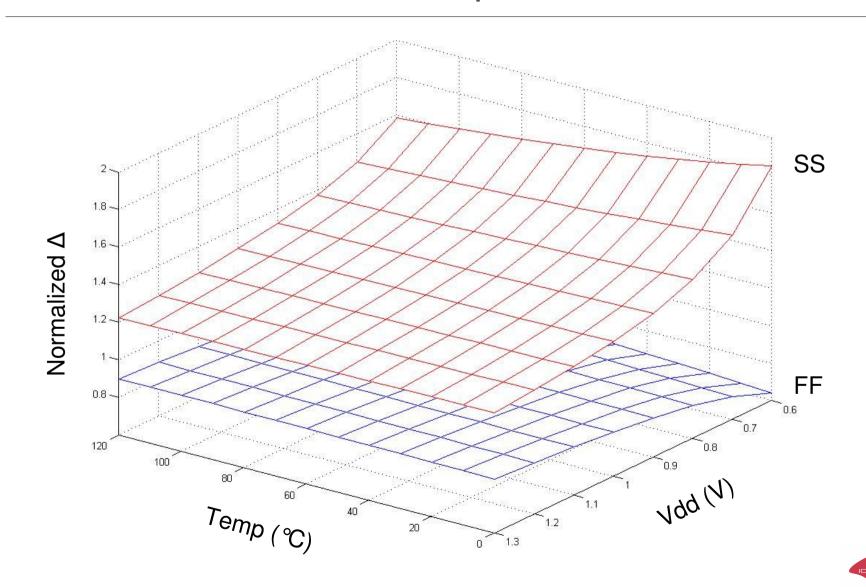

# Manufacturing Spread: 65nm mid V<sub>T</sub> LOP Delay

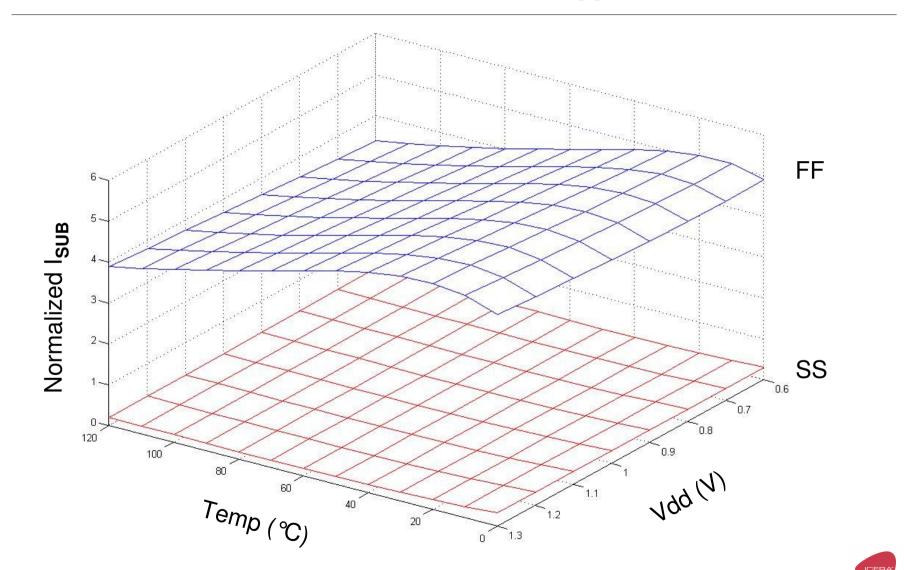

# Manufacturing Spread: 65nm mid V<sub>T</sub> LOP I<sub>SUB</sub>

simon@icerasemi.com

# Optimality of Design

## Power, Money and Performance

#### Excellent recent work on Power vs Performance (among many)...

- Srinivasan, Brooks, Gschwind, Bose, Zyuban, Strenski and Emma, "Optimimum Pipelines for Power and Performance", Micro '02.

- Zyuban and Strenski, "Unified Methodology for Resolving Power-Performance Tradeoffs at the Microarchitectural and Circuit Levels", ISLPED '02.

- Harstein, Puzak, "Optimum Power/Performance Pipeline Depth", Micro '03.

- Dao, Zeydel, Oklobdzija, "Energy Optimization of Digital Pipelined Systems Using Circuit Sizing and Supply Scaling", Trans. VLSI Systems '05.

But outside the computer market, few chips sell on MHz.

Most designs set out to minimize cost (and power) at fixed performance...

- Decode an MPEG video without glitching.

- Execute an ADSL modem at 8Mbps.

- etc...

CERA

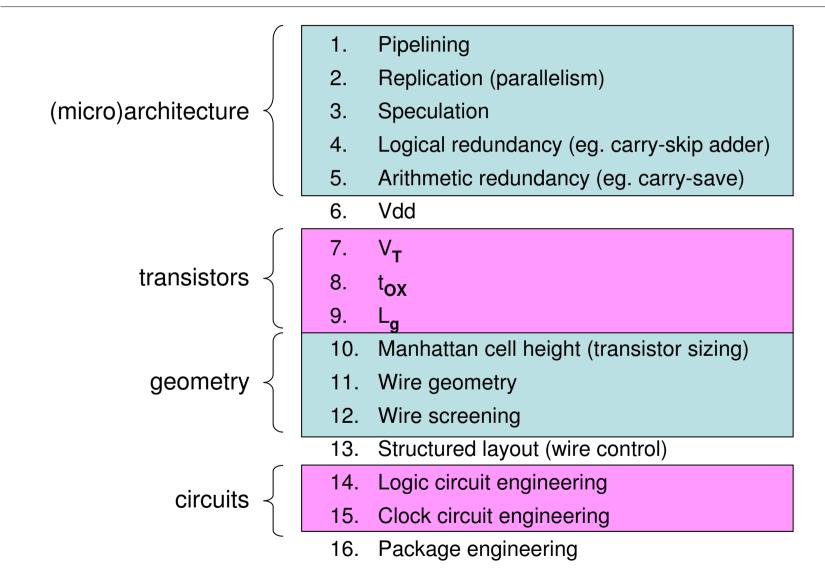

### **Design Levers**

ICERA

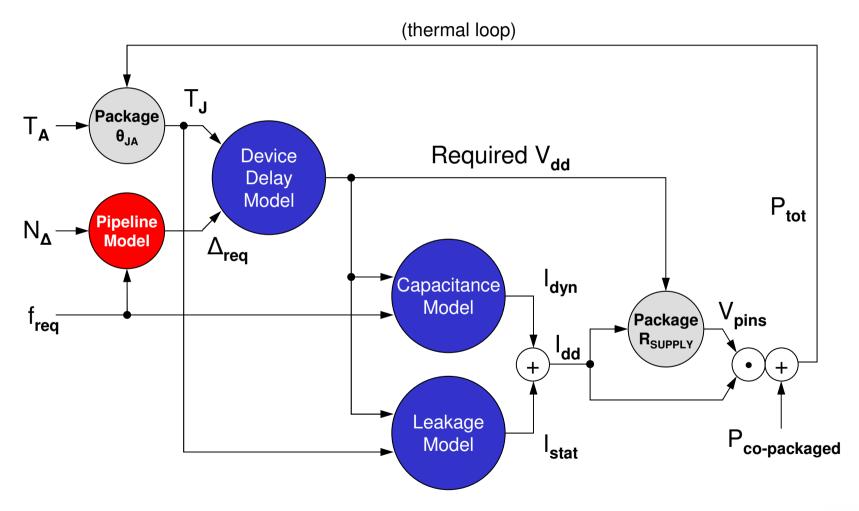

#### Electro-Thermal Model

## Pipeline Model

#### K "pipettes"...

Chip...

non-pipeline latches

pipelined logic

RAM

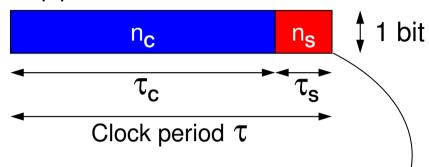

Average n<sub>c</sub> transistors of combinatorial logic per pipe stage per pipeline bit.

ns transistors per pipeline latch.

Units of  $\tau$  are "i"  $\equiv$  "FO4"; 1i =  $\Delta$  seconds.

Arbitrary width/depth mix of pipettes make up the pipelined logic.

Define...

Flux  $\Phi = n_c / \tau_c$  (T/i/b)

Performance  $\Psi = Kn_{c}f$  (T/s)

Cost  $N = K(n_c + n_s)$  (T)

Frequency  $f = 1/\tau\Delta$  (Hz)

### Reality not Included...

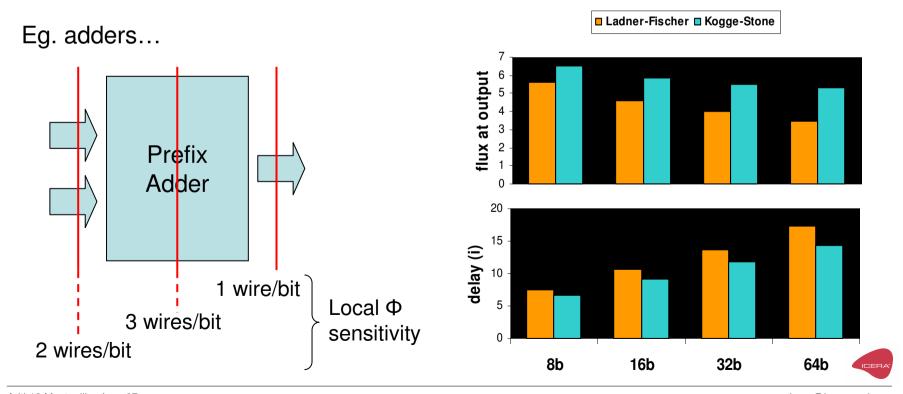

- Performance  $\Psi$  ( $T_{\text{COMB}}/s$ ) tends to over-state effective performance at low  $\tau$ , because logical redundancy is introduced to speed up logic paths and mitigate latency by speculation.

- Flux  $\Phi$  (T/i/b) varies a lot locally; tends to rise at low  $\tau$  for the same redundancy reason, and because pipe cuts have less freedom to avoid high-flux logic.

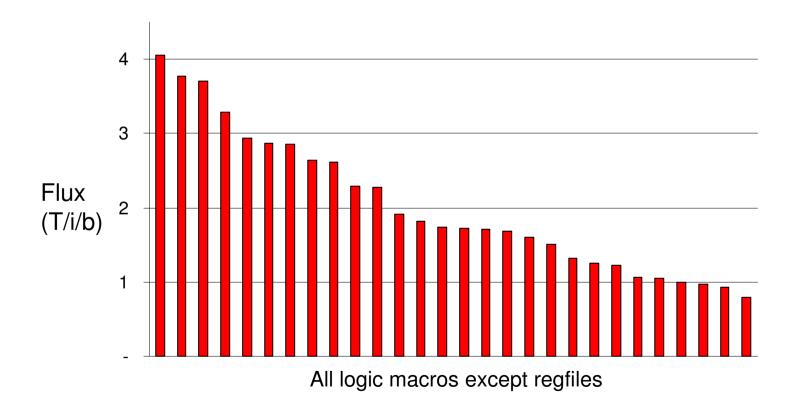

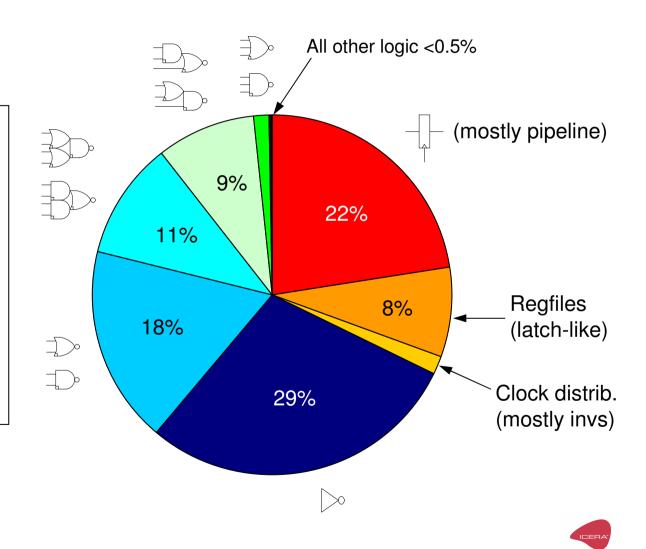

## Pipeline Flux in Icera's DXP®

- $\Phi$  ~ 3-4 for arithmetic and random translation logic.

- $\Phi$  ~ 1-2 for steering logic.

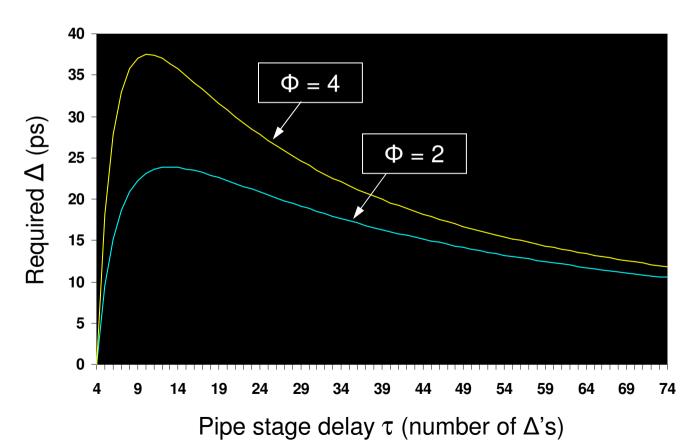

## Required Δ to meet specified Performance Ψ and Cost N

$$\Delta_{\text{required}} = \left(\frac{N}{\Psi \tau}\right) / \left(1 + \frac{n_S}{\Phi(\tau - \tau_S)}\right)$$

#### **Specification**

Latch delay 4i Latch cost 40T Performance 10PT/s Design Cost 10MT

# Constant Flux Implications ( $\Phi = 3$ , $\tau_s = 4i$ )

## DXP® Logic Stage Population, by #Transistors

Manhattan cells are ubiquitous in all digital design methodologies.

Complex cells can be important for performance but account for negligible % of total transistors.

Designs are characterized (capacitance, leakage, delay, area) by a few simple Manhattan stages.

# The Design Hull

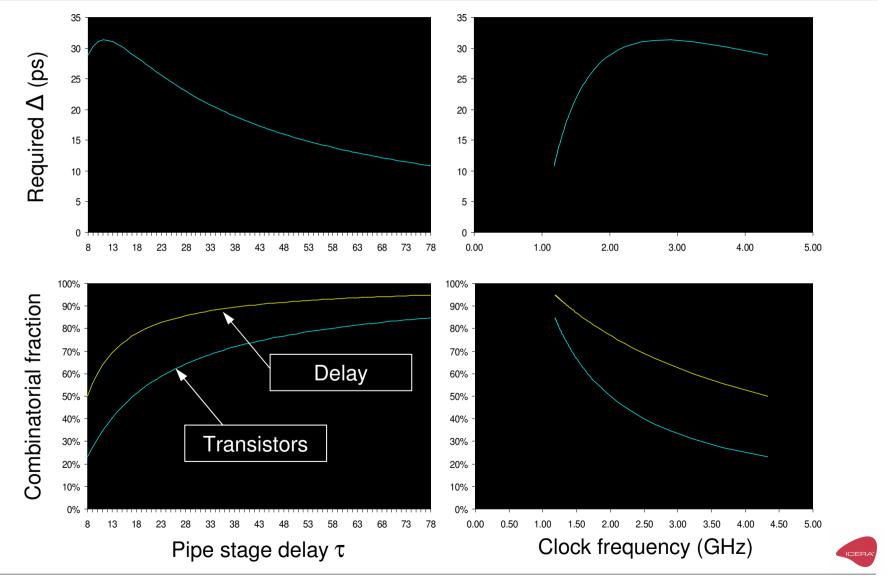

## Example Design Spec

Performance  $\Psi = 15PT/s$

Flux  $\Phi = 4T/i/b$

Latch Cost  $n_s = 40T$

Latch Delay  $\tau_s = 4i$

Non-Pipe Logic = 5MT

RAM = 1MB

Latch Activity = 3x Combinatorial Activity

RAM Activity = 0.2x Combinatorial Activity

65nm high V<sub>T</sub> LOP Process

Ambient Temp = 85 ℃

Max Die Temp = 125 ℃

Package  $\theta_{JC} = 15 \,^{\circ}\text{C/W}$

Supply  $R = 50m\Omega$

Fixed Parasitic Power = 100mW

Vdd Limit Range = 0.7V - 1.2V

Arith18 Montpellier June 07

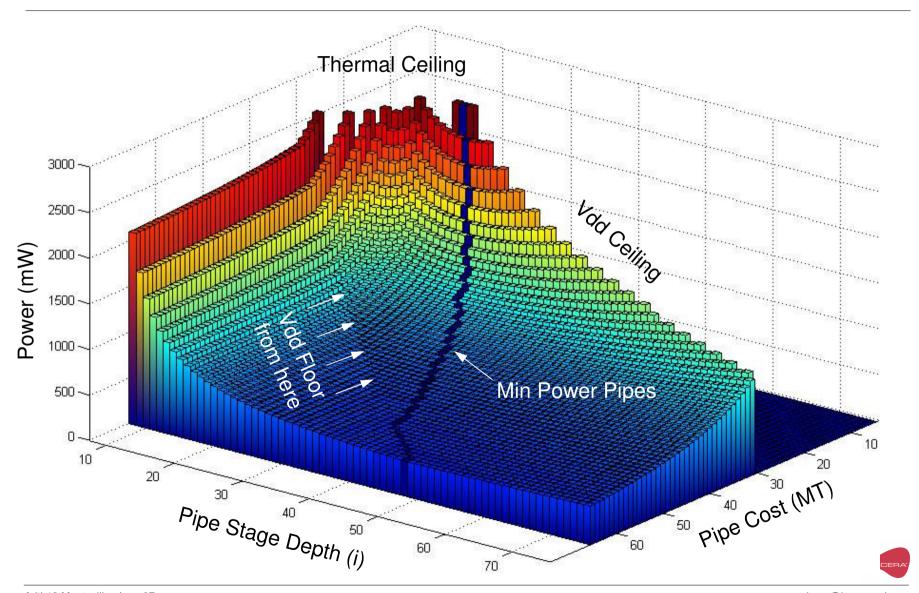

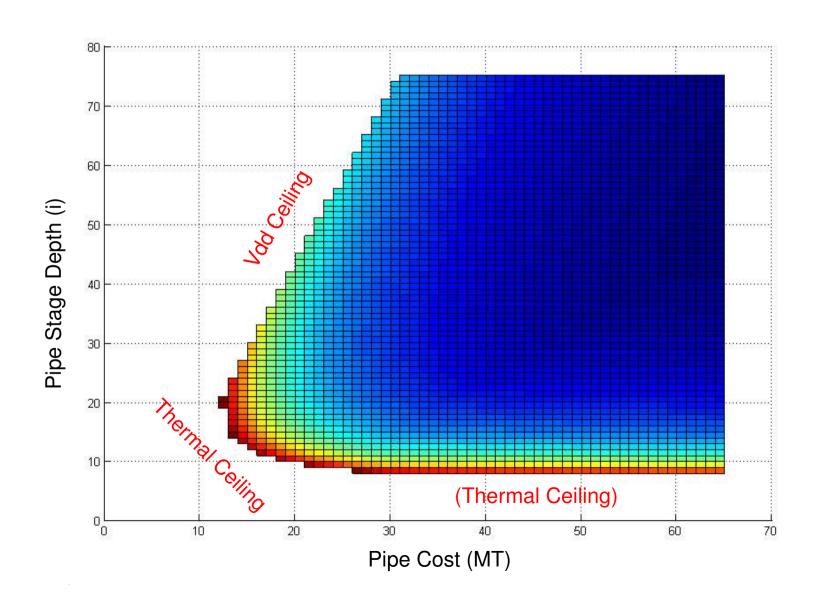

# Design Hull

# Feasible Designs

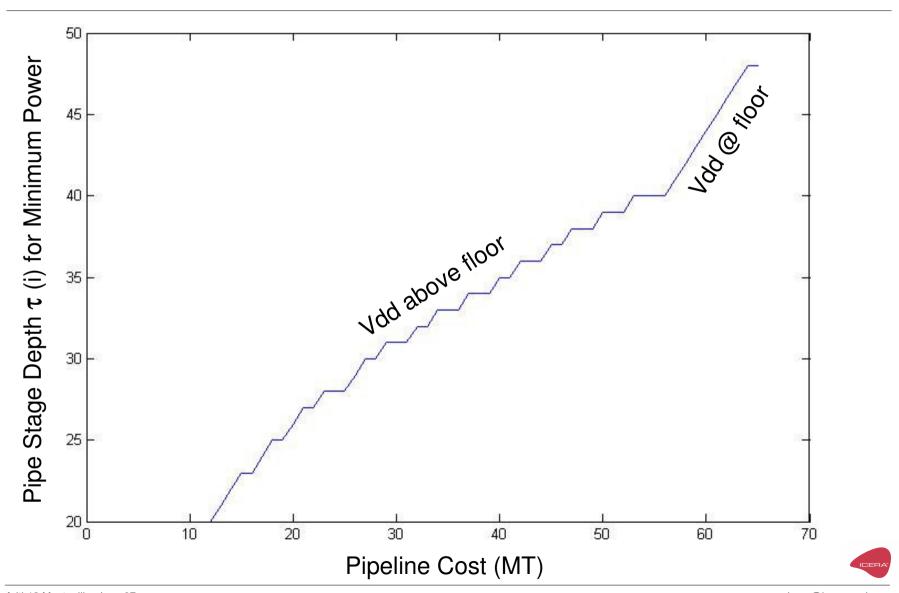

## Minimum Power Pipelines

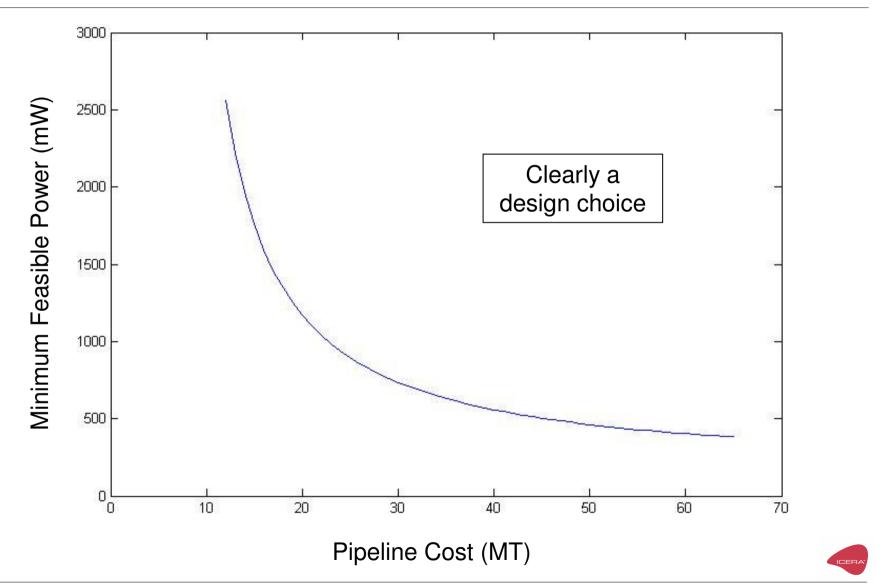

## The Cost of Minimizing Power

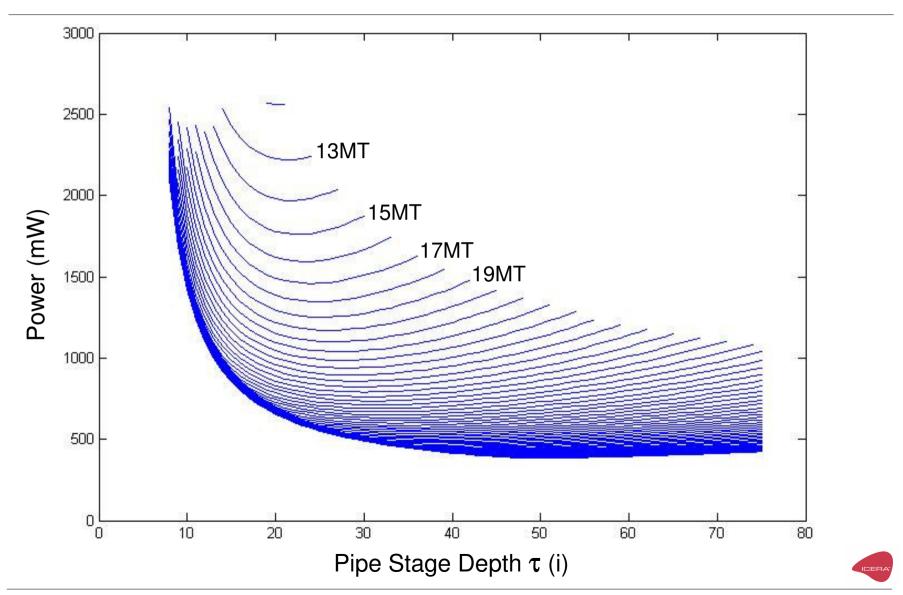

# Minimum Power Pipelines

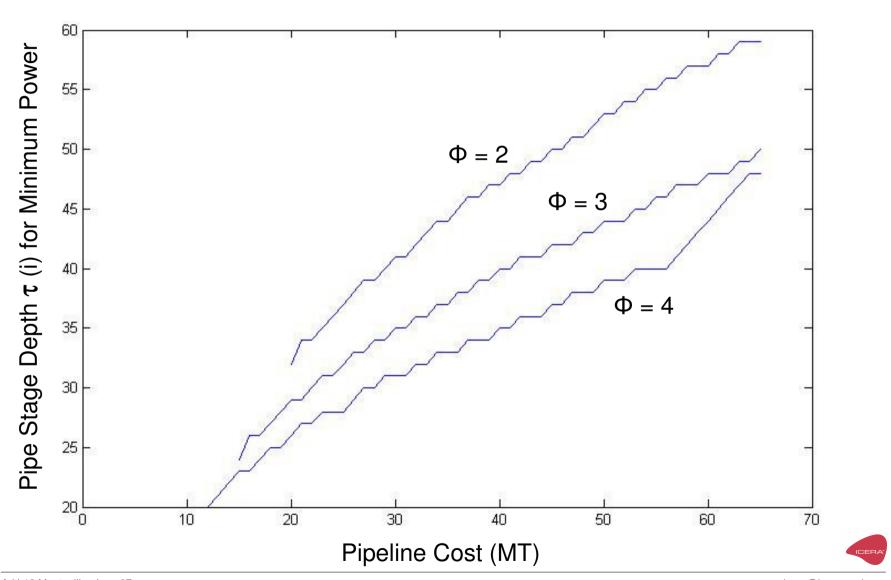

# Sensitivity to Pipeline Flux

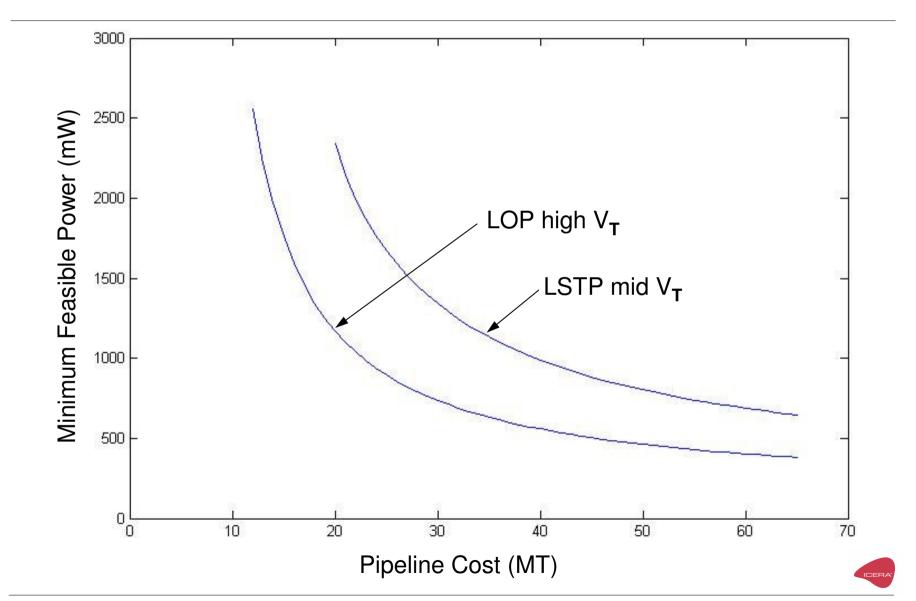

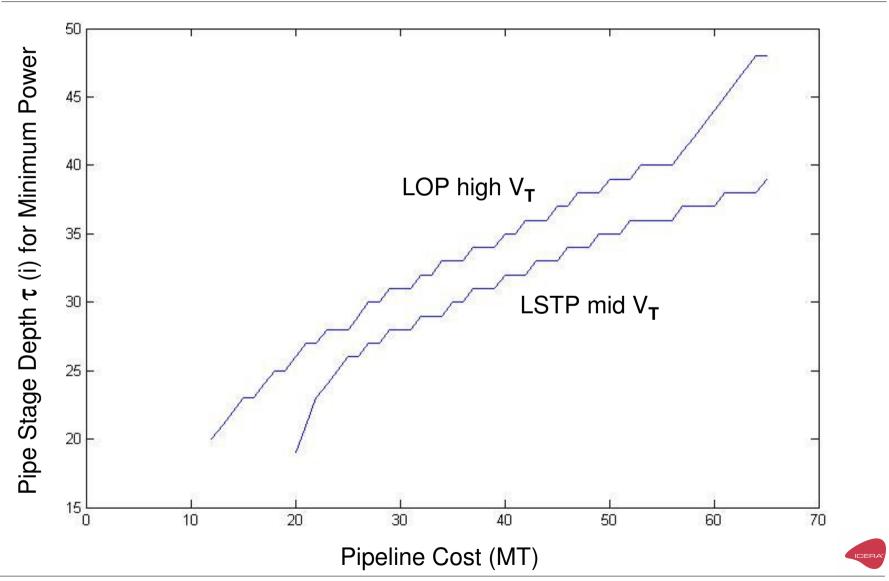

### LOP vs LSTP

### LOP vs LSTP

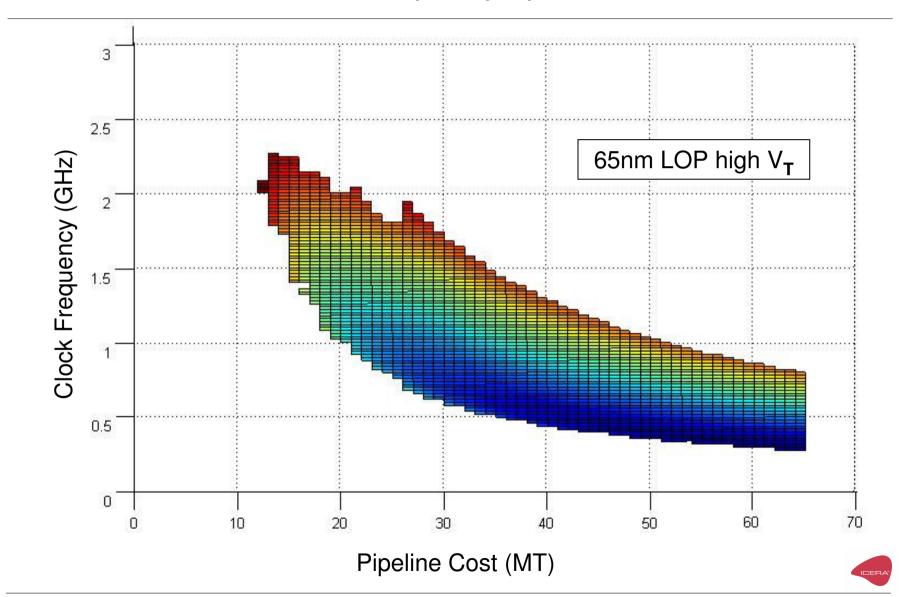

# Feasible Solutions in Cost-Frequency Space

simon@icerasemi.com

Arith18 Montpellier June 07

# Implications for Design

## Implications for Chip Design

#### Every logic chip will have control over its supply voltage.

- Integrated regulators?

- Switch off in standby limited call for LSTP processes?

We can't minimize cost and power simultaneously.

Good cost-power points require fairly high speed.

Beyond synthesis and auto-P&R today → more Structured Custom?

Short pipelines expose the basic TA assumption (single path sensitization).

- Wavefront timing analysis tools?

- Voltage agility makes TA sign-off harder.

### Structured Custom

Natural cell placement by engineers...

...is enough for predictable auto-routing

ICERA

## Thank You

# Enjoy the Symposium ©