## PhD Position NXP Semiconducteur-LIRMM

## Built-in-Self-Repair in the Design Step Context

Academic Supervision : Serge Bernard, Michel Renovell, Mariane Comte et Florence Azaïs, LIRMM

**Industrial Supervision :** Benoit Agnus, Vincent Fresnaut, Philippe Cauvet, NXP Semiconductors France

## **Host Team :**

- Institute for System Testing, the Joint Institute ISyTest between the laboratory of informatics, robotics and Microelectronics of Montpellier (LIRMM) and NXP Semiconductors Caen (SiP Program)

Location: 50% at LIRMM Montpellier, 50% at NXP Caen

## Abstract

The market of semiconductors is driven by the need of more and more services in one product. While the complexity and the heterogeneous of the micro-systems are significantly increasing, the required time-to-market of these new complex systems becomes very short. Moreover, the present and future semiconductor technologies allow better and better performances but become very sensitive to process variations and to the final environment. This economical and technical context makes design of integrate circuits and systems challenging. An interesting solution to help design and to allow high manufacturing yield consists in adding some auto-calibration capabilities onto the chip to be able to improve the system performances after manufacturing. These solutions would allow in-situ parameter correction during the life of the circuit to offset possible drifts.

Test techniques are dedicated to detect failures in integrated circuits or systems during their manufacturing. Auto-calibration techniques are based on the same principle of the detection of non-expected specification but with a specific circuitry to correct it if possible. Our objective is to develop and adapt new test techniques to propose a complete auto-calibration or Built-in-Self-Repair (BISR) solutions.

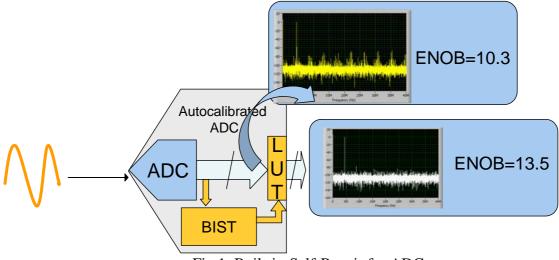

As illustration, let us consider BISR technique for Analog-to-Digital Converters (fig.1). The design of ADCs is very critical but unfortunately these components are necessary present in every multimedia or telecommunication system. The idea is to relax some design constraints in order to meet the required time to market and to enhance some parameters after manufacturing by digital post processing on the digital output codes.

Fig.1: Built-in-Self-Repair for ADC

The first step of the proposed PhD position will consist in defining the design criteria according to the end-user application (frequency, resolution...). The second step of the work will consist in studying and evaluate the existing solutions of calibration techniques.

Then, the robustness and the reliability of the chosen technique will be evaluated according to the final environment of the product (power supply variations, temperature, input and sampling frequency...).

Based on this case study, the PhD student will try to define a specific design flow allowing the possible BISR integration for design constraint relaxation.

Another objective will be to extend this approach of digital post processing for design constraint relaxation to new kind of circuits (Mixed-Signal or RF).

Contacts: <u>bernard@lirmm.fr</u> <u>benoit.agnus@nxp.com</u> <u>philippe.cauvet@nxp.com</u>