## Polytech'Montpellier - ERII 4 M2 EEA - Systèmes Microélectroniques

Circuits Intégrés Analogiques

Chapitre I

Technologie de fabrication des Circuits Intégrés

Pascal Nouet - Septembre 2009

nouet@lirmm.fr

### Objectif

- Comprendre l'enchaînement des étapes de fabrication d'un procédé CMOS

- Etapes élémentaires de fabrication

- Simulation de la fabrication

- Formation des locos / zones actives (obsolète)

- auto-alignement des diffusions

- Etude de l'enchaînement de ces étapes dans le cas d'un inverseur CMOS

- Apprendre à « lire » un layout

- Illustration avec un outil de TCAD (SILVACO)

- Comportements parasites et fiabilité

- Les composants passifs

## Plan

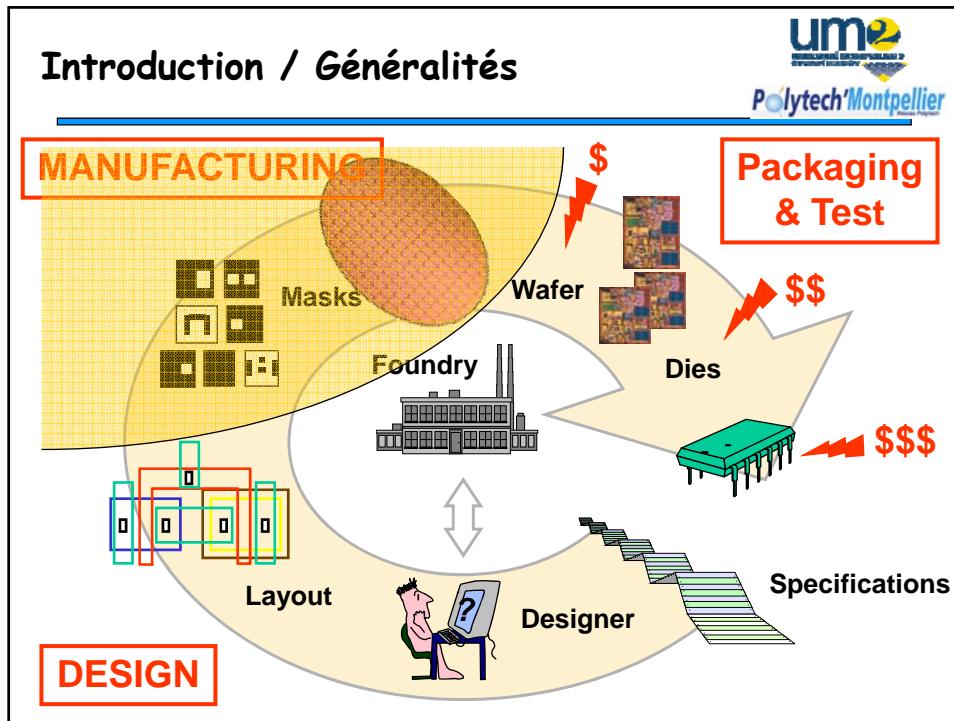

- Introduction / généralités

- Procédé CMOS

- étapes élémentaires

- simulation de la fabrication d'un transistor

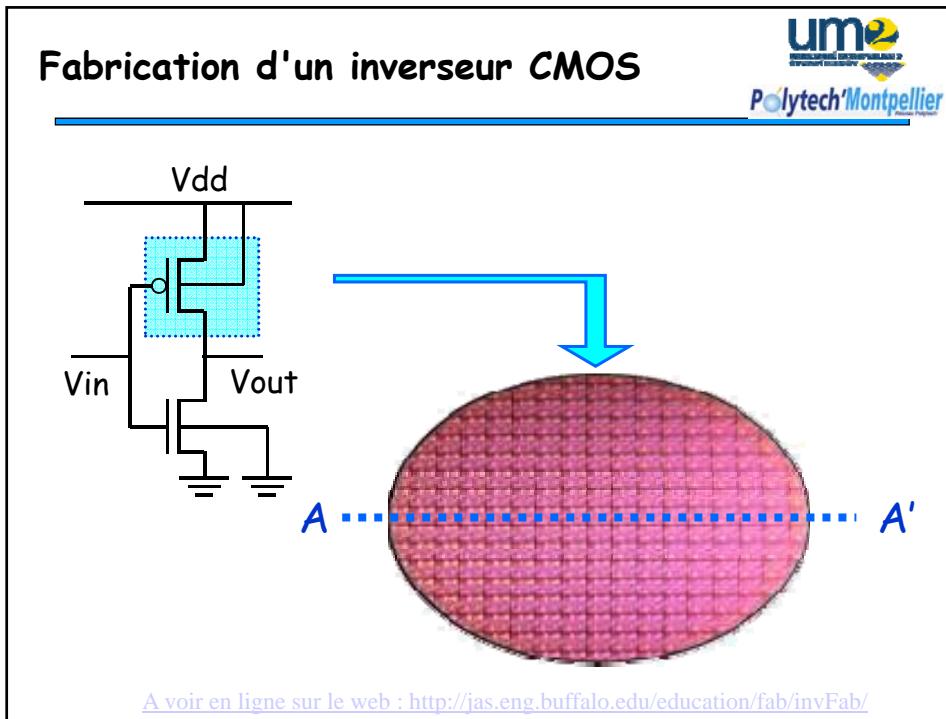

- fabrication d'un inverseur CMOS

- Layout et masques de fabrication

- Procédé CMOS et comportements parasites

- Composants Passifs

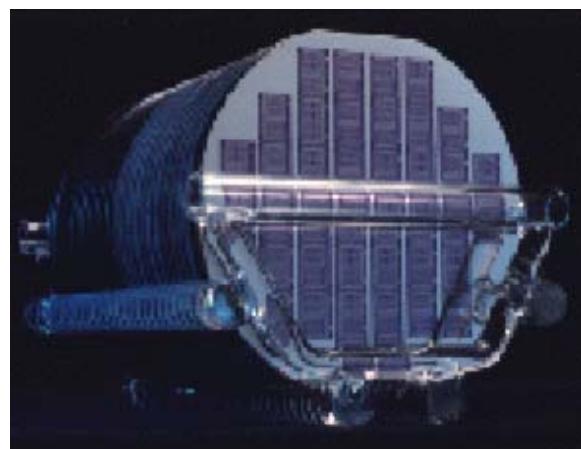

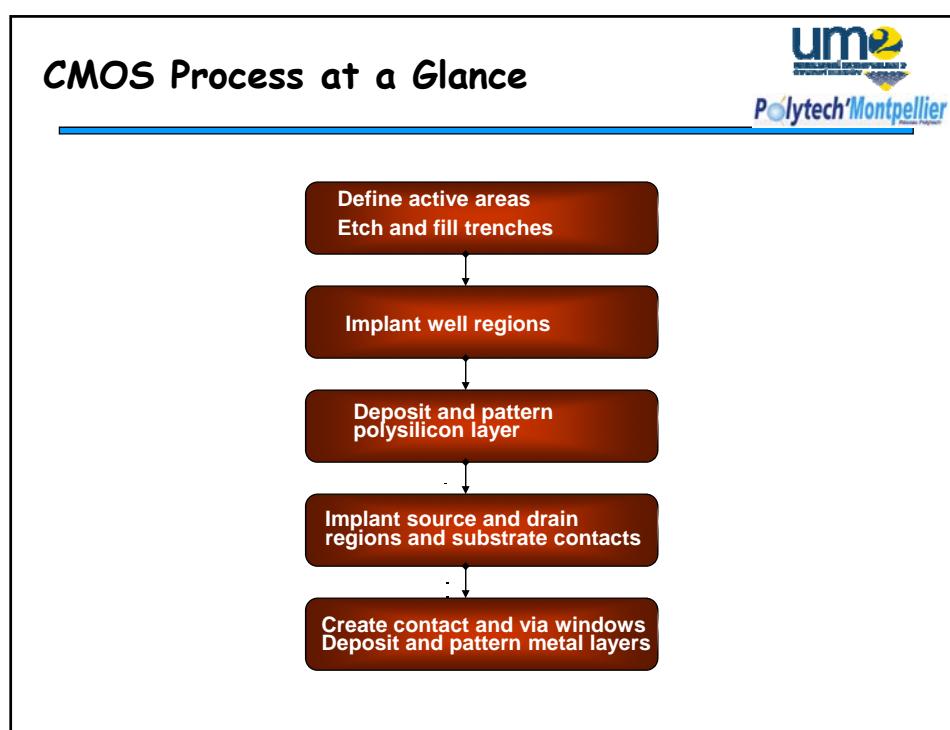

## Procédé CMOS

- Le circuit intégré est obtenu par une succession d'étapes technologiques simples faisant appel à la lithographie

- Fabrication par lots

- Reproductible

- Grands volumes

- Automatisé

- Le jeu de masques est le niveau de description ultime d'un circuit intégré

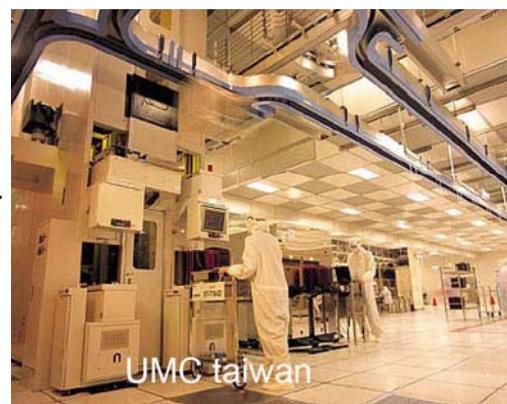

UMC taiwan

## Procédé CMOS : étapes élémentaires

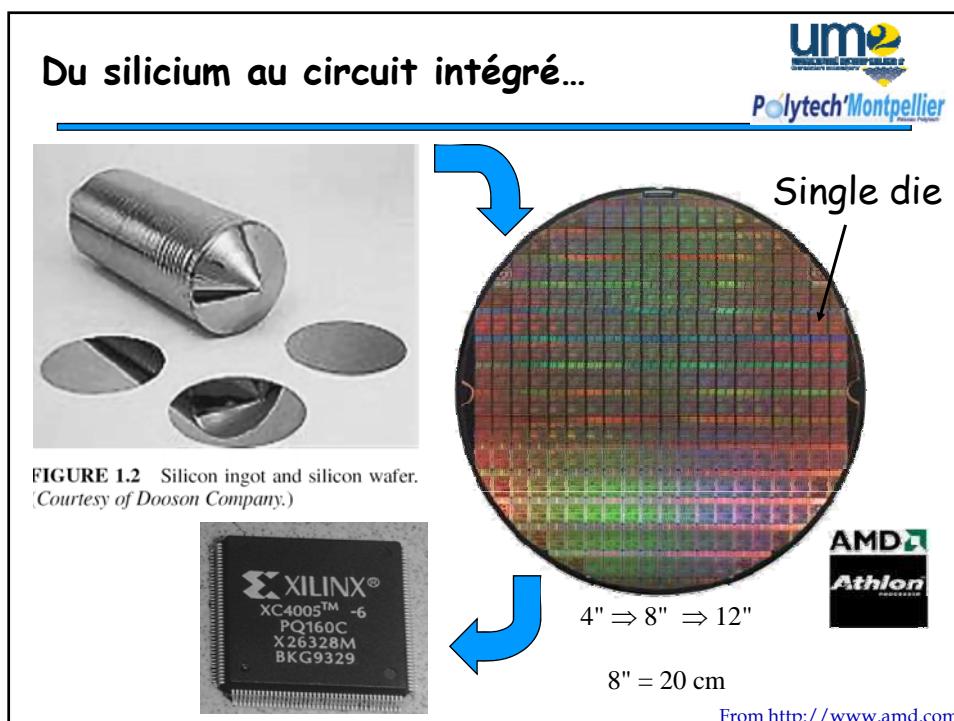

**Tirage et Découpage du Silicium**

$4'' \Rightarrow 8'' \Rightarrow 12''$

$8'' = 20 \text{ cm}$

## Procédé CMOS : étapes élémentaires

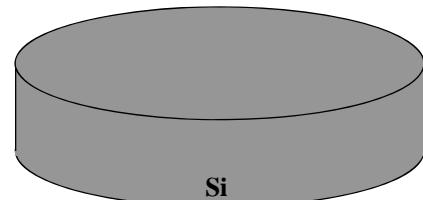

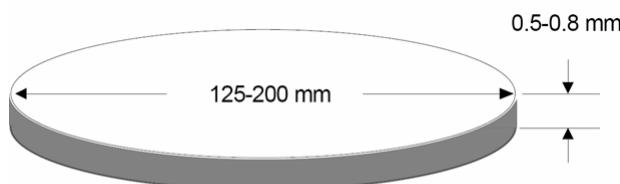

**Wafer, Substrat, Disque de Silicium**

n-type:  $3\text{-}5 \Omega\text{-cm}$

p-type:  $14\text{-}16 \Omega\text{-cm}$

$4'' \Rightarrow 8'' \Rightarrow 12''$

$8'' = 20 \text{ cm}$

## Procédé CMOS : étapes élémentaires

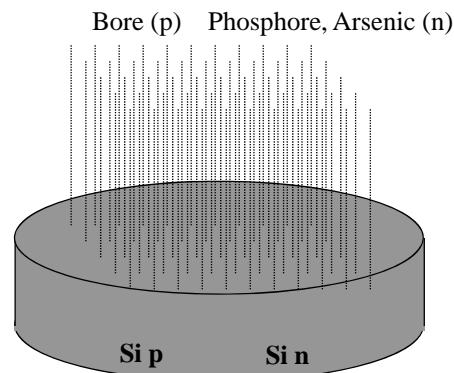

### Implantation ionique

## Procédé CMOS : étapes élémentaires

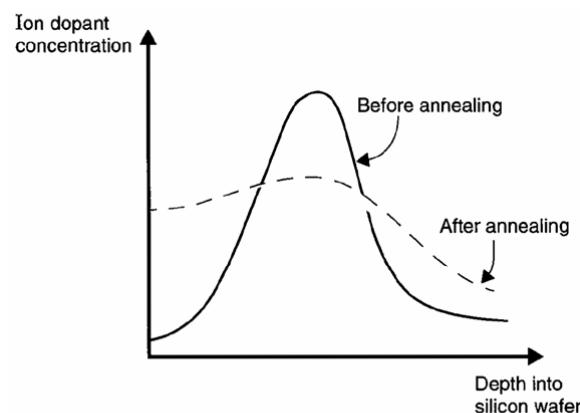

### Annealing    $900^{\circ}\text{C} - 1100^{\circ}\text{C}$ (15-30 minutes)

**Fig. 2.4** Dopant profiles after ion implantation both before and after annealing.

## Procédé CMOS : étapes élémentaires

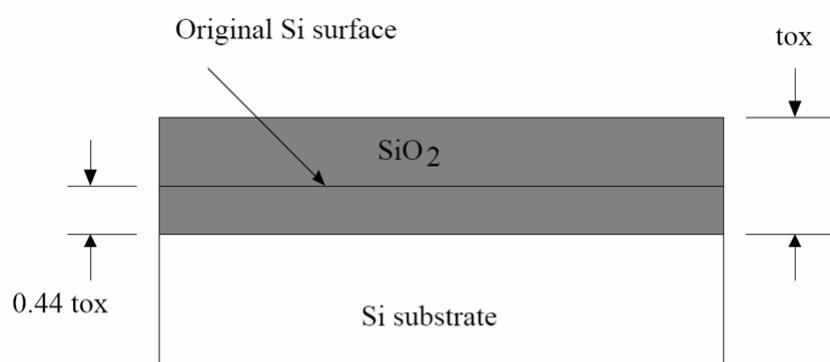

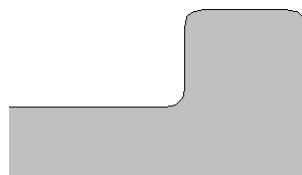

### Oxydation

## Procédé CMOS : étapes élémentaires

### Oxydation

## Procédé CMOS : étapes élémentaires

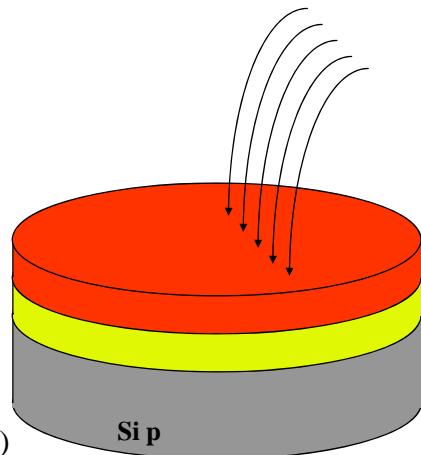

### Déposition

- Silicon nitride ( $\text{Si}_3\text{N}_4$ )

- Silicon dioxide ( $\text{SiO}_2$ )

- Aluminum

- Polysilicon

- Chemical-vapor deposition (CVD)

- Low-pressure chemical-vapor deposition (LPCVD)

- Plasma-assisted chemical-vapor deposition (PECVD)

- Sputter deposition

## Procédé CMOS : étapes élémentaires

### Métallisation

## Procédé CMOS : étapes élémentaires

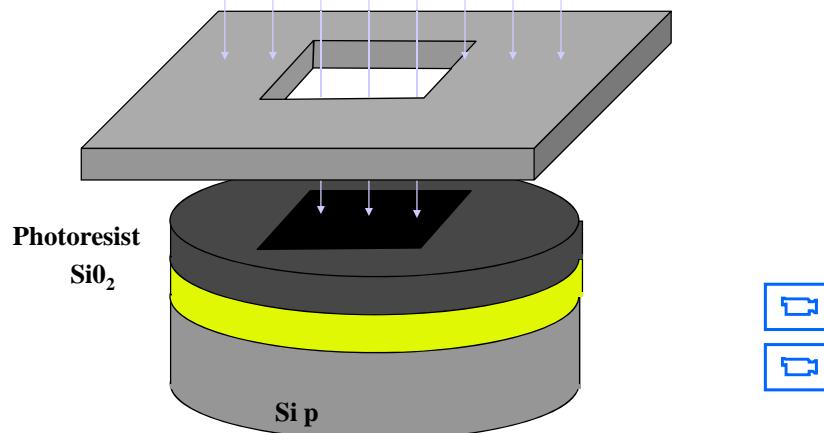

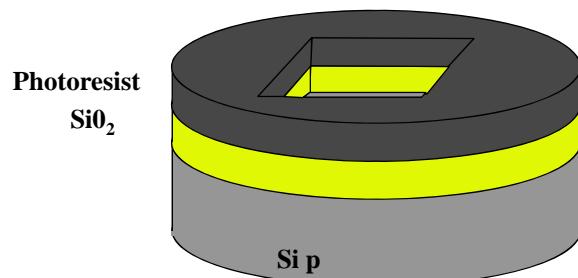

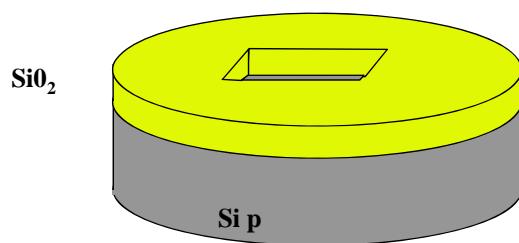

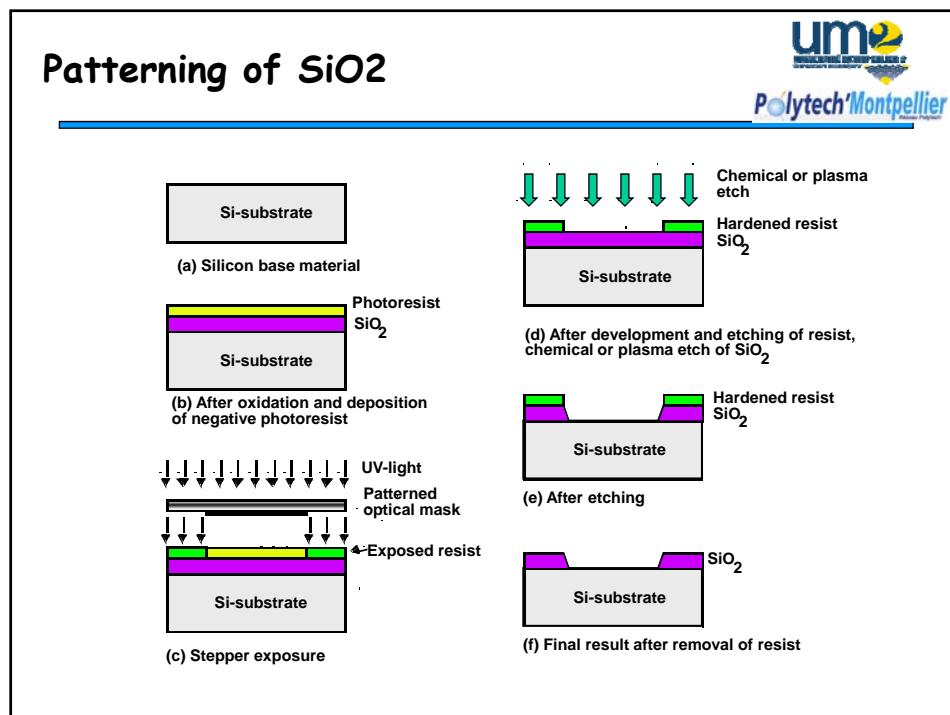

### Photolithographie

## Procédé CMOS : étapes élémentaires

### Photolithographie

## Procédé CMOS : étapes élémentaires

Diffusion      Gaz (2PH<sub>3</sub>+4O<sub>2</sub>) + 1000°C

Alternative : Implantation Ionique + Annealing

## Procédé CMOS : étapes élémentaires

### Découpage des puces

## Plan

---

- Introduction / généralités

- Procédé CMOS

- étapes élémentaires

- simulation de la fabrication d'un transistor

- fabrication d'un inverseur CMOS

- Layout et masques de fabrication

- Procédé CMOS et comportements parasites

- Composants Passifs

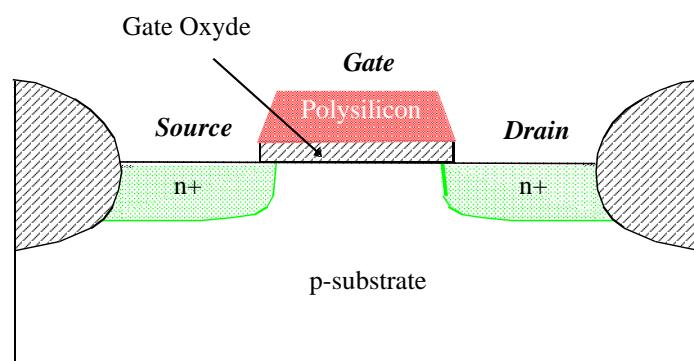

## Simulation de la fabrication d'un transistor

---

- Transistor MOS de type N

*Bulk Contact*

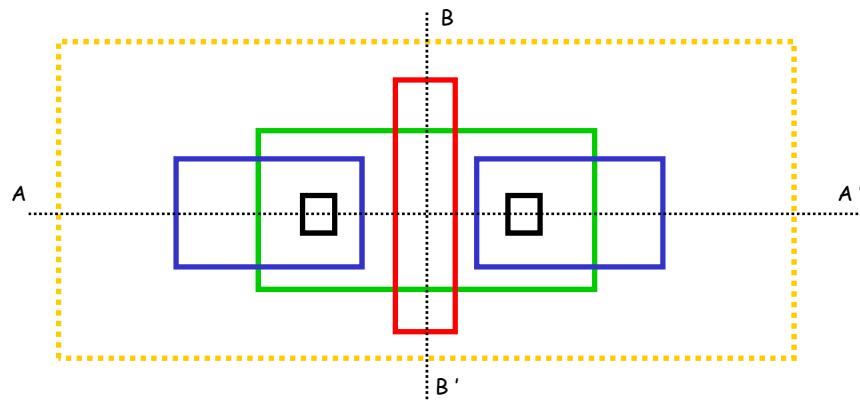

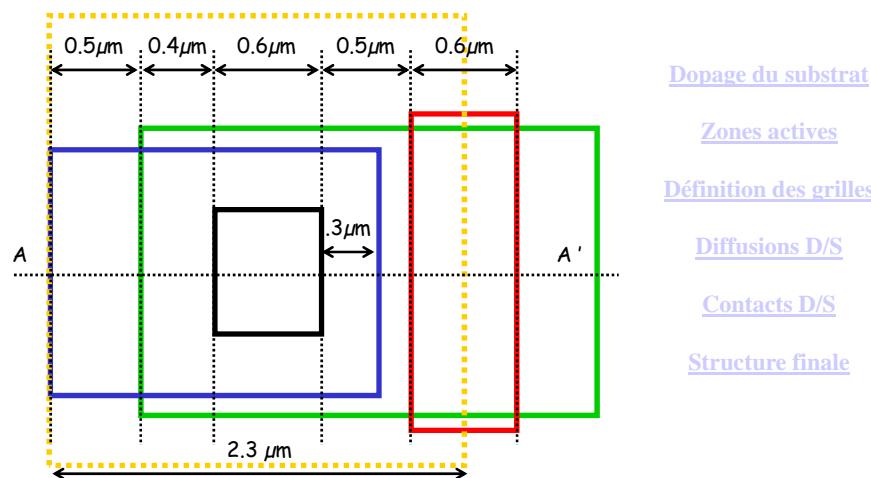

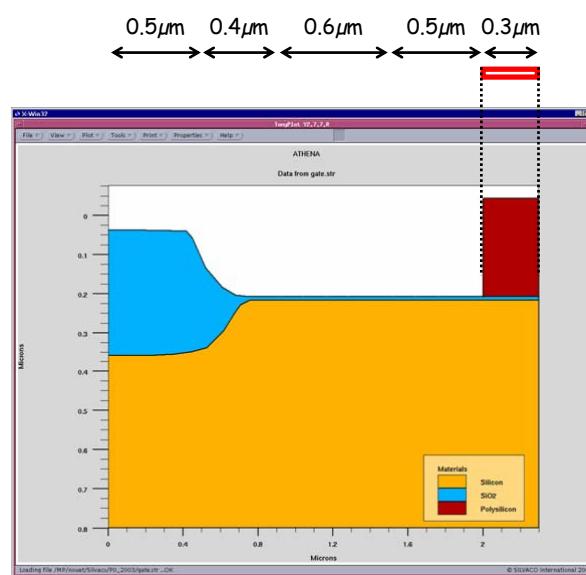

## Simulation de la fabrication d'un transistor

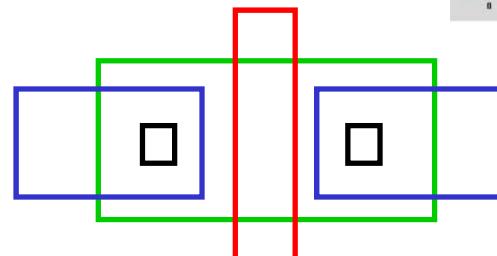

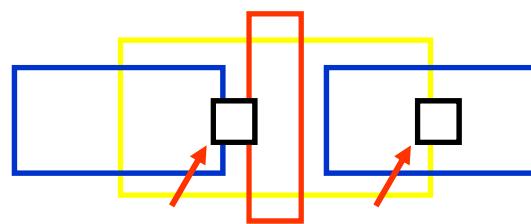

- Layout/masques d'un transistor MOS de type N

- Simulation 2D => axe AA'

- Symétrie de la structure (axe BB')

## Simulation de la fabrication d'un transistor

- Prise en compte des règles de dessin (AMS 0.6 $\mu$ m)

## Simulation de la fabrication d'un transistor

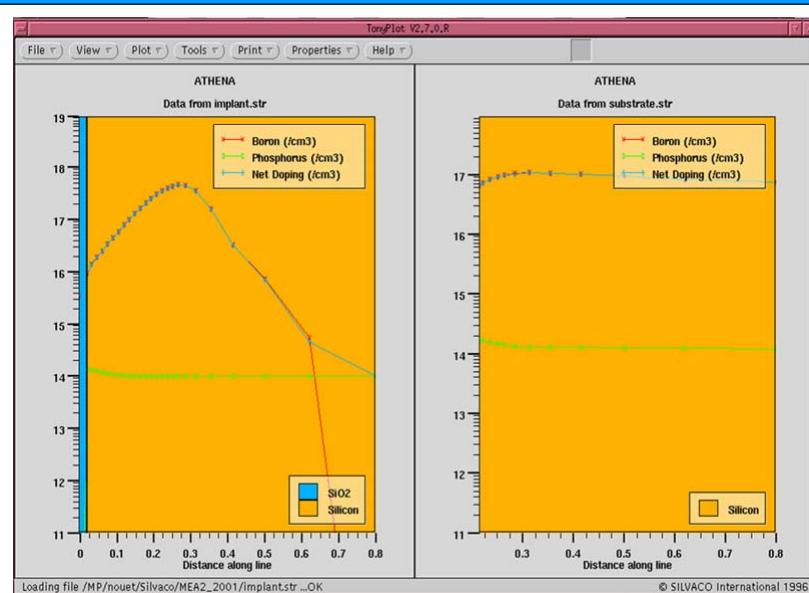

- Dopage du substrat P (1D)

- choix d'un substrat, orientation, concentration d'impuretées

- implantation ionique bore (=accepteur) à travers un oxyde

- Visualisation du résultat en 1D : dopage après implantation

- Diffusions des dopants, oxydation de la surface puis nettoyage

- Visualisation du résultat après dopage

### Dopage du substrat (1D)

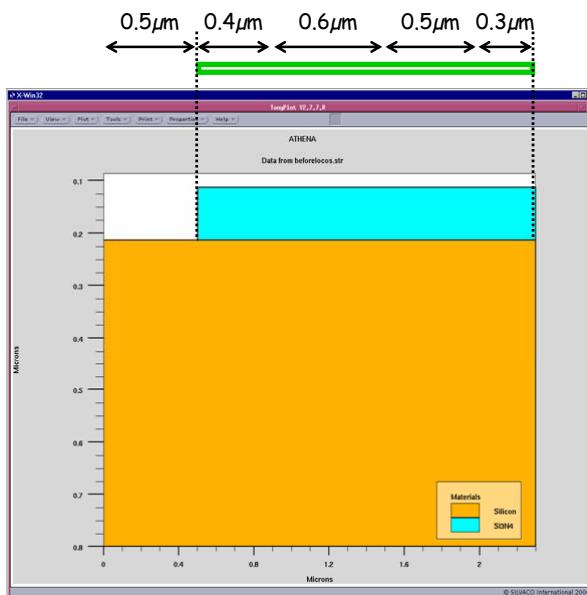

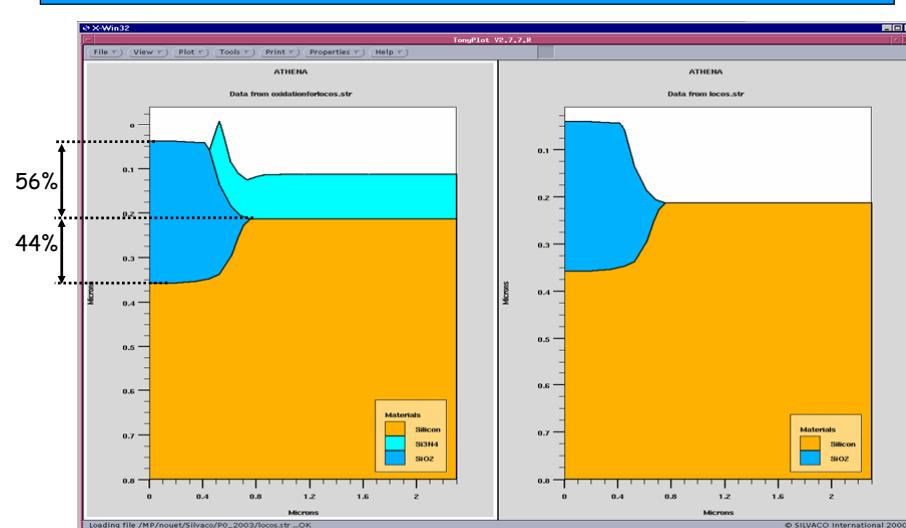

## Définition des zones actives (1/2)

## Définition des zones actives (2/2)

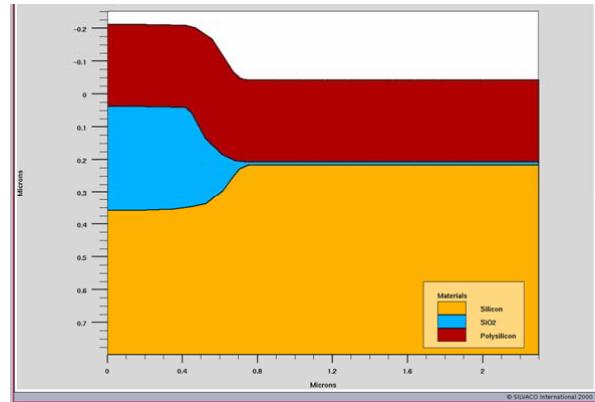

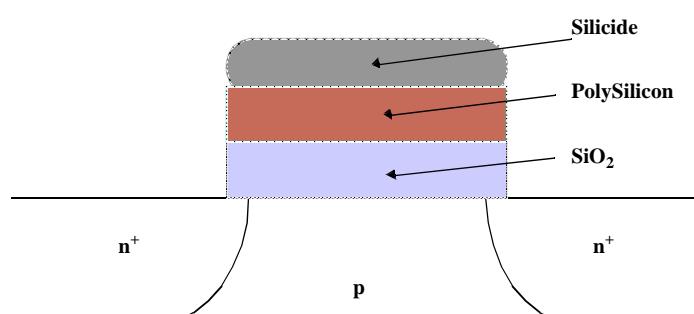

## Réalisation des grilles (1/2)

- Croissance de l'oxyde de grille (oxydation sèche)

- Dépôt polysilicium - Réalisation de la grille

## Réalisation des grilles (2/2)

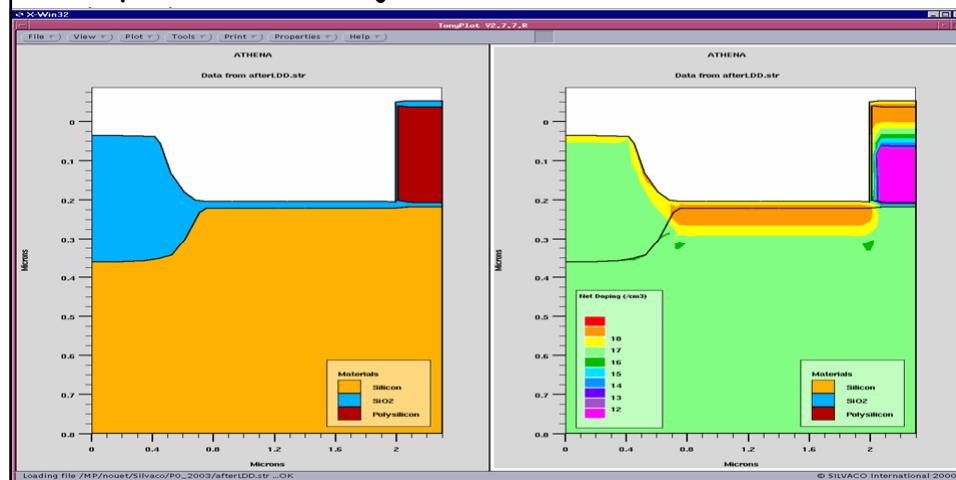

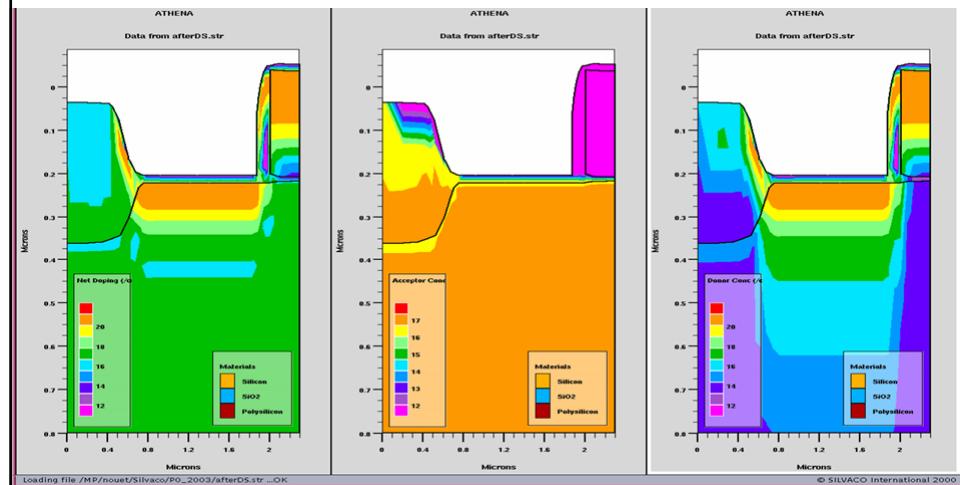

## Réalisation des diffusions D/S (1/3)

- Oxydation de la surface puis première implantation des jonctions D/S en donneurs

## Réalisation des diffusions D/S (2/3)

- Réalisation des spacers

## Réalisation des diffusions D/S (3/3)

- Implantation finale des diffusions en donneurs (arsenic)

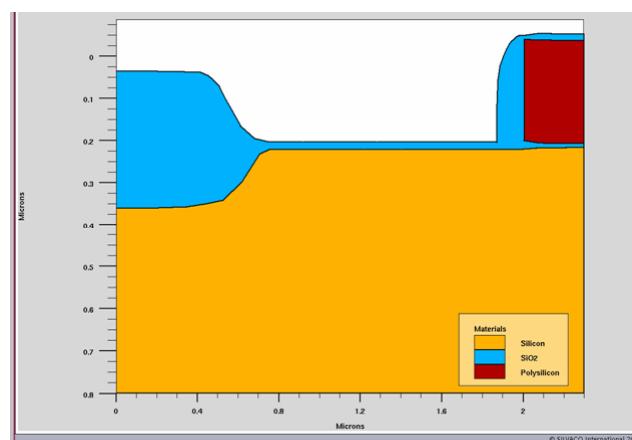

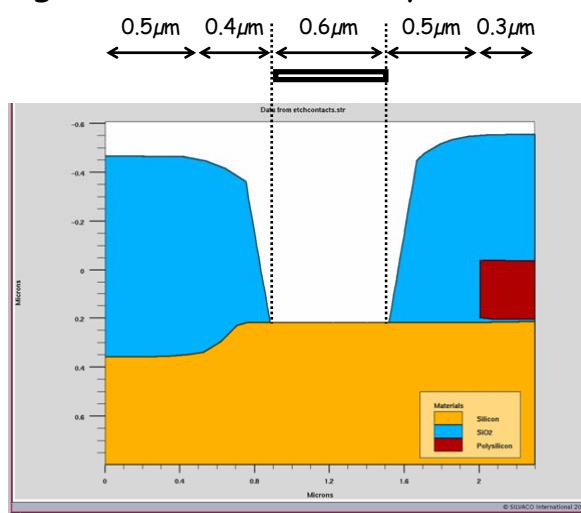

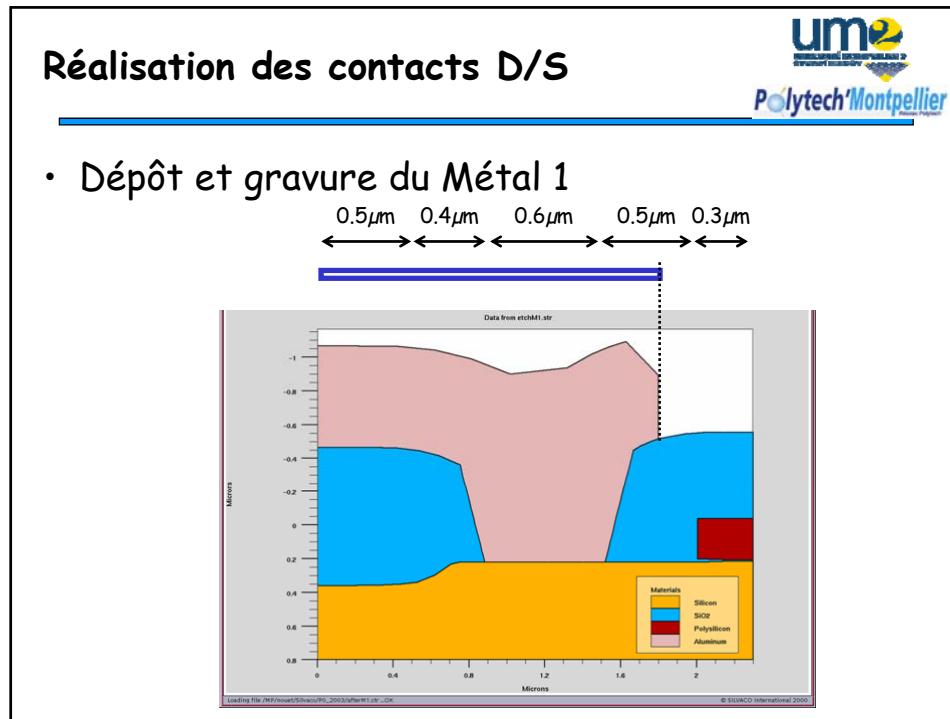

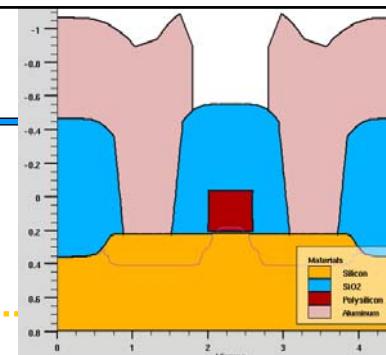

## Réalisation des contacts D/S

- Dépôt et gravure de l'oxide Poly-Métal 1

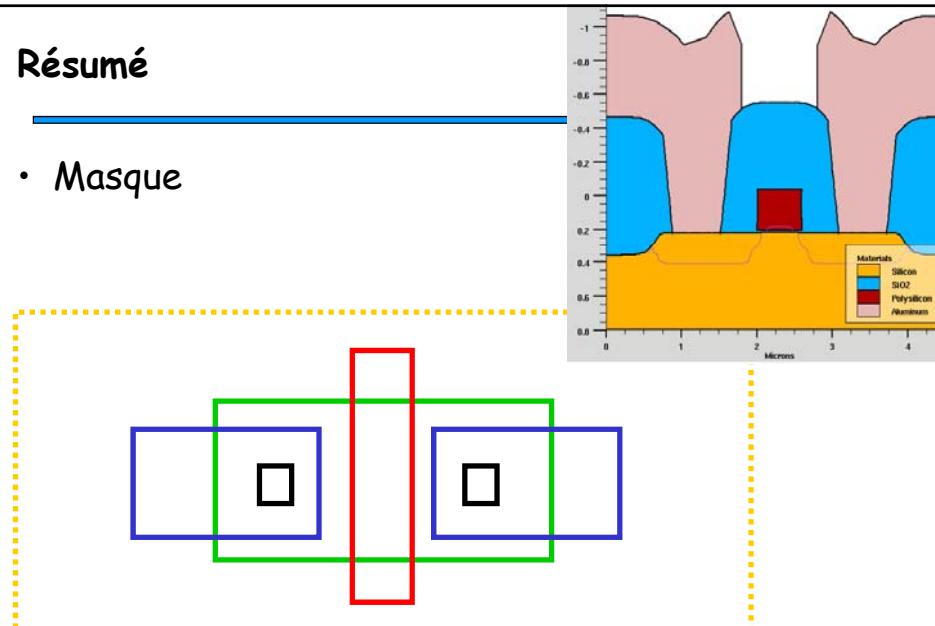

## Résumé

- Masque

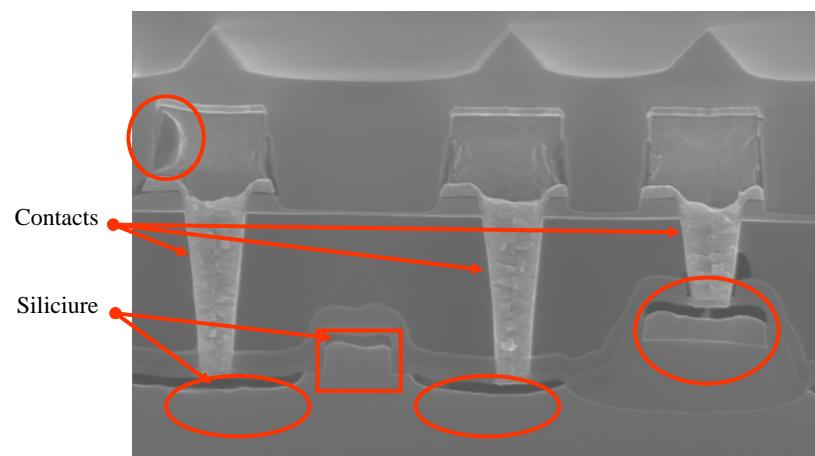

## Etat de l'art

### Évolution des technologies

| Taille ( $\mu\text{m}$ ) | 2   | 1   | 0.8 | 0.5 | 0.35 | 0.25 | 0.18  | 0.13  |

|--------------------------|-----|-----|-----|-----|------|------|-------|-------|

| Oxyde (Ang.)             | 400 | 200 | 150 | 100 | 70   | 50   | 35-70 | 27-65 |

**LDD**

**Silicium**

**STI**

**Cu**

## Etat de l'art

## Plan

- Introduction / généralités

- Procédé CMOS

- étapes élémentaires

- simulation de la fabrication d'un transistor

- fabrication d'un inverseur CMOS

- Layout et masques de fabrication

- Procédé CMOS et comportements parasites

- Composants Passifs

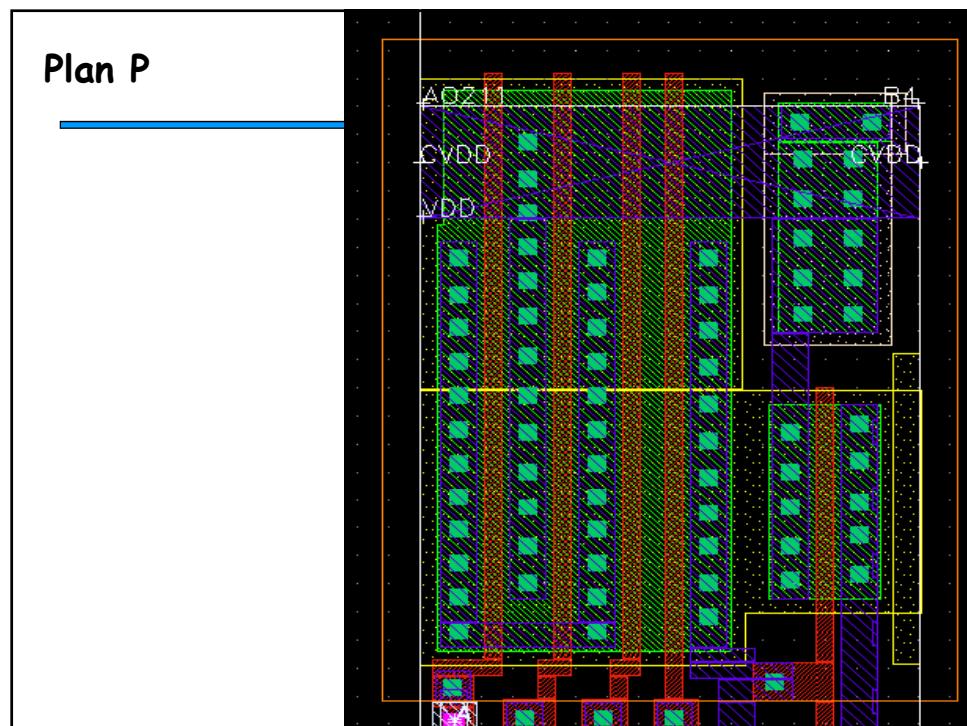

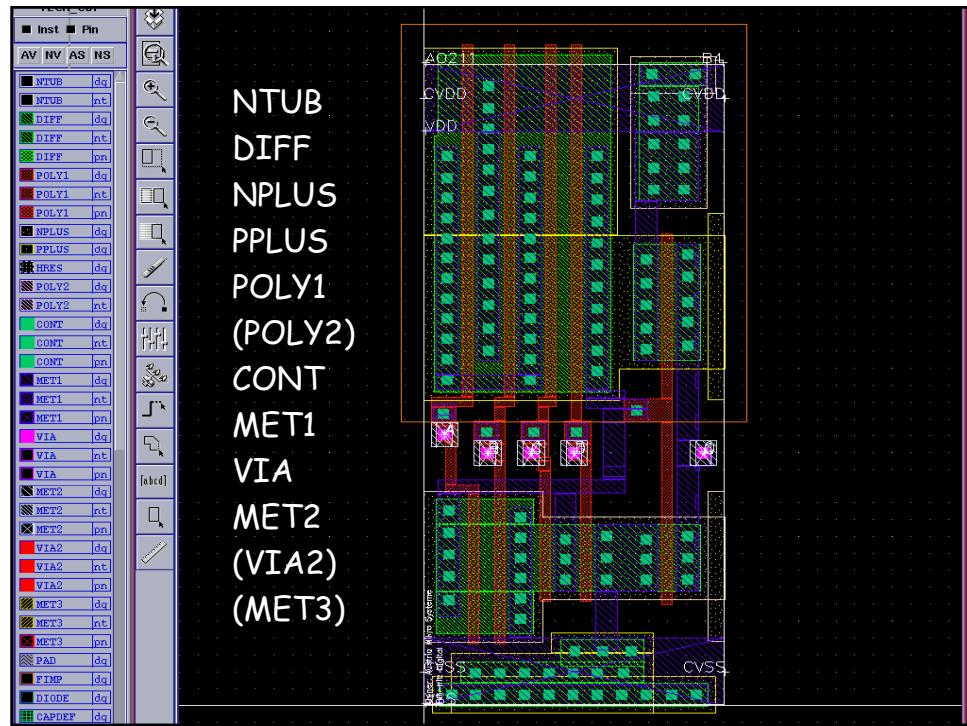

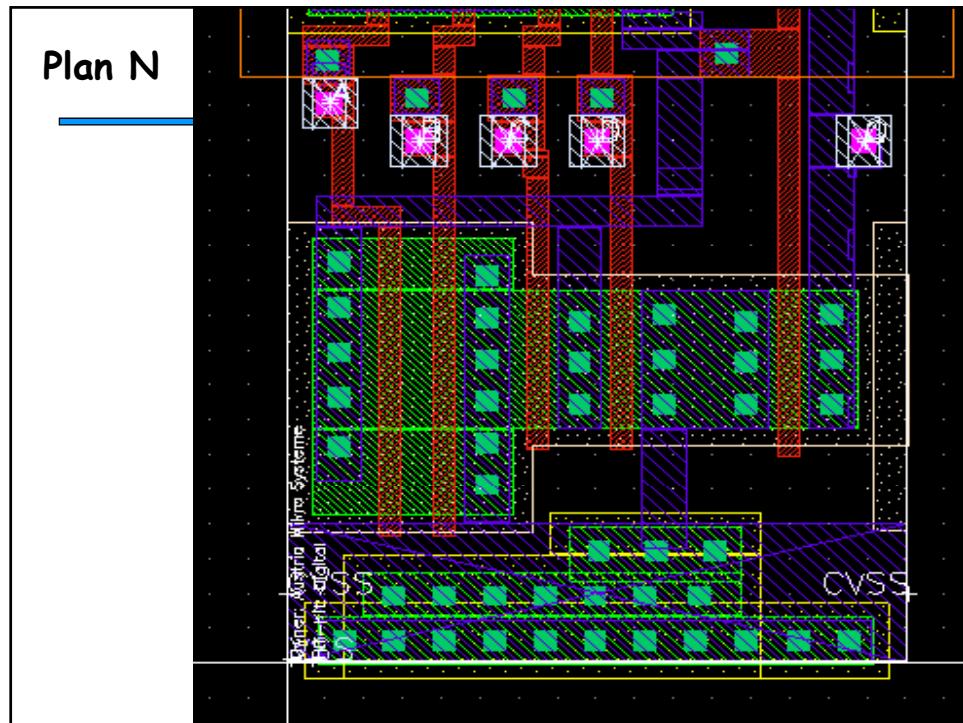

## Plan

- Introduction / généralités

- Procédé CMOS

- Layout et masques de fabrication

- Application : réalisation d'un inverseur MOS

- Règles de dessin et layout

- Application : analyse de layout

- Procédé CMOS et comportements parasites

- Composants Passifs

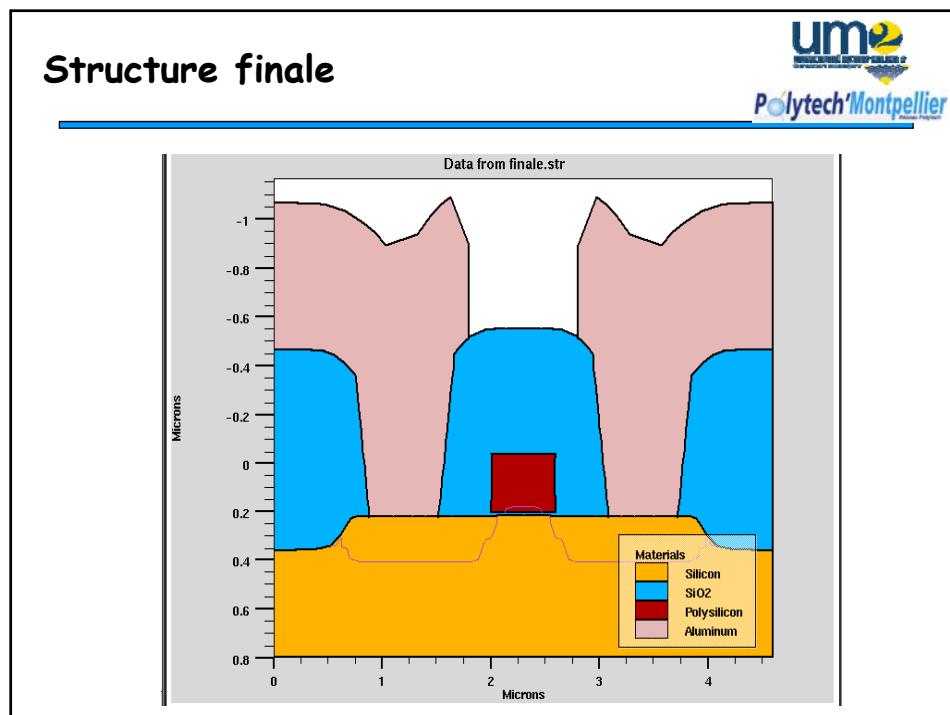

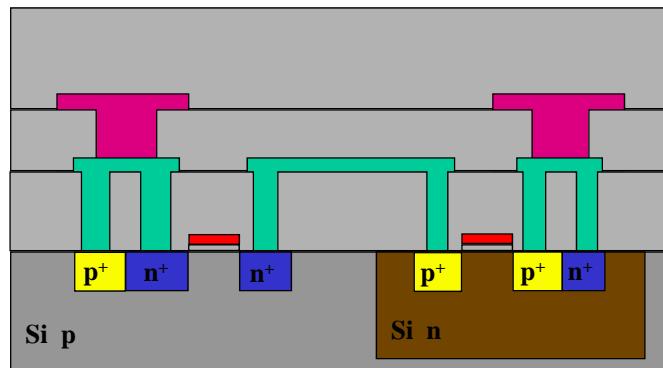

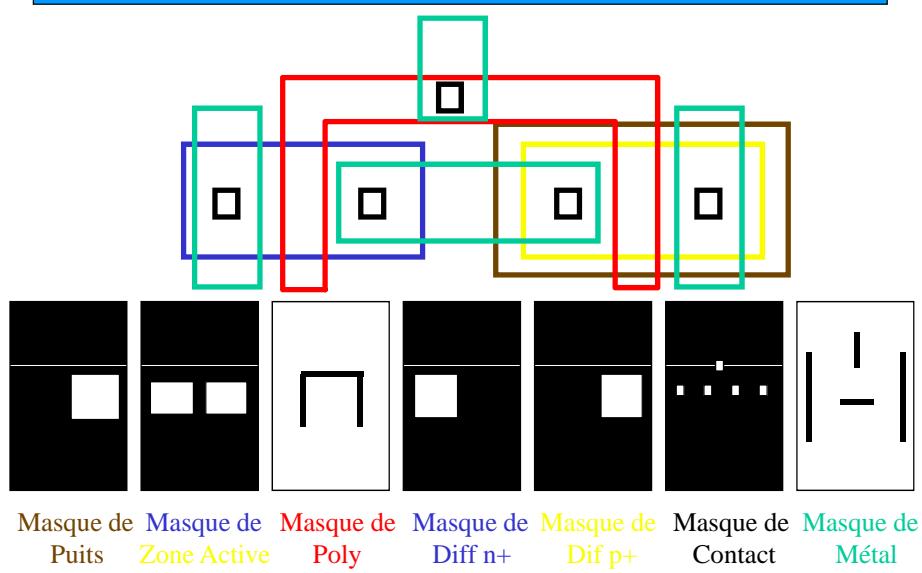

## Application : réalisation d'un inverseur CMOS

## Application : réalisation d'un inverseur CMOS

## Application : réalisation d'un inverseur CMOS

## Plan

- Introduction / généralités

- Procédé CMOS

- Layout et masques de fabrication

- Application : réalisation d'un inverseur MOS

- Layout et règles de dessin

- Application : analyse de layout

- Procédé CMOS et comportements parasites

- Composants Passifs

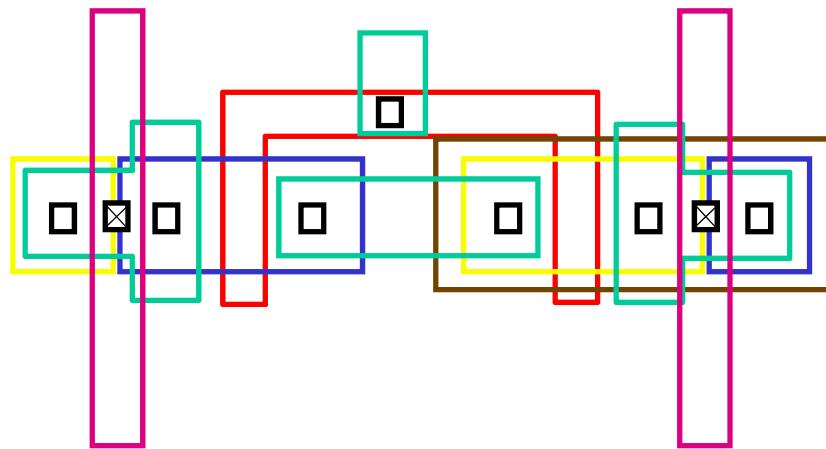

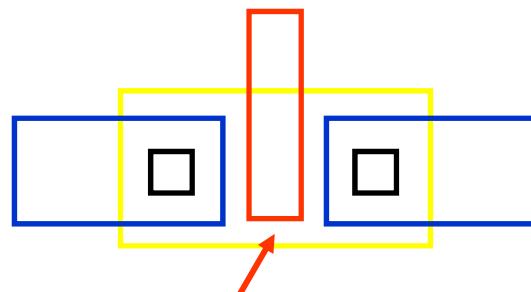

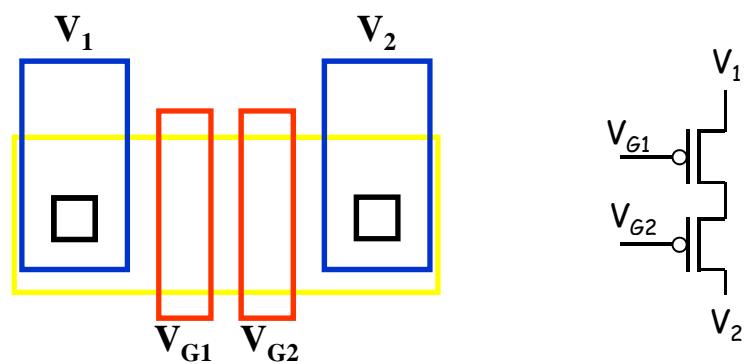

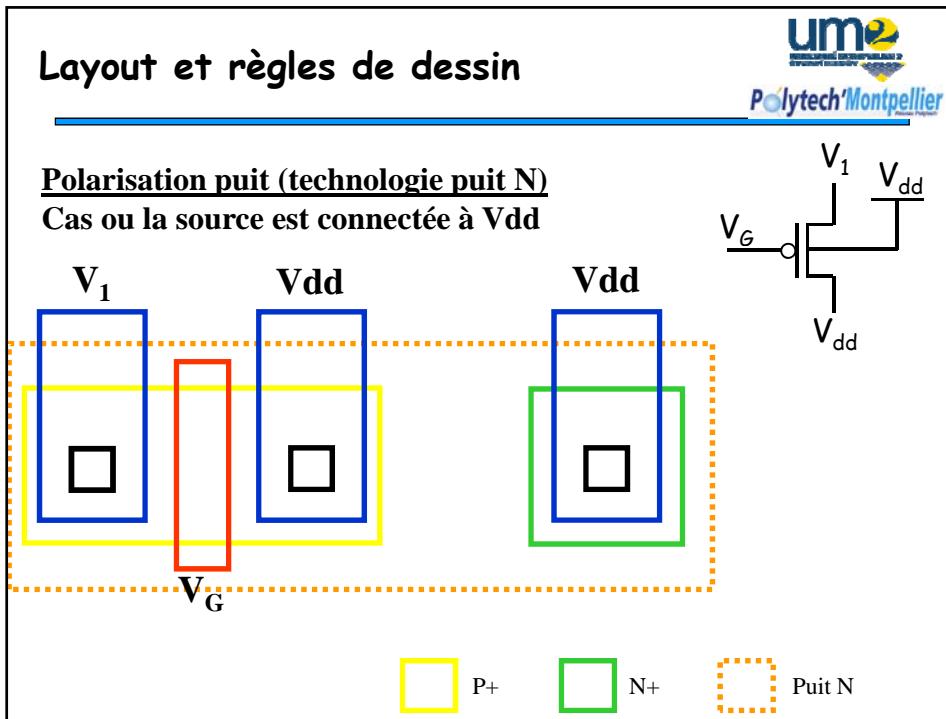

## Layout et règles de dessin

### Conséquences d'un désalignement des masques

## Layout et règles de dessin

### Conséquences d'un désalignement des masques

## Layout et règles de dessin

## Solutions préventives : les règles de dessin

## Layout et règles de dessin

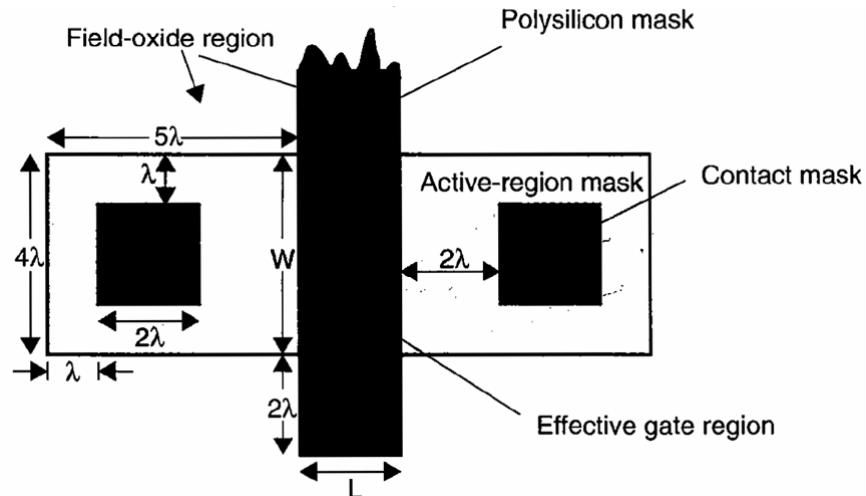

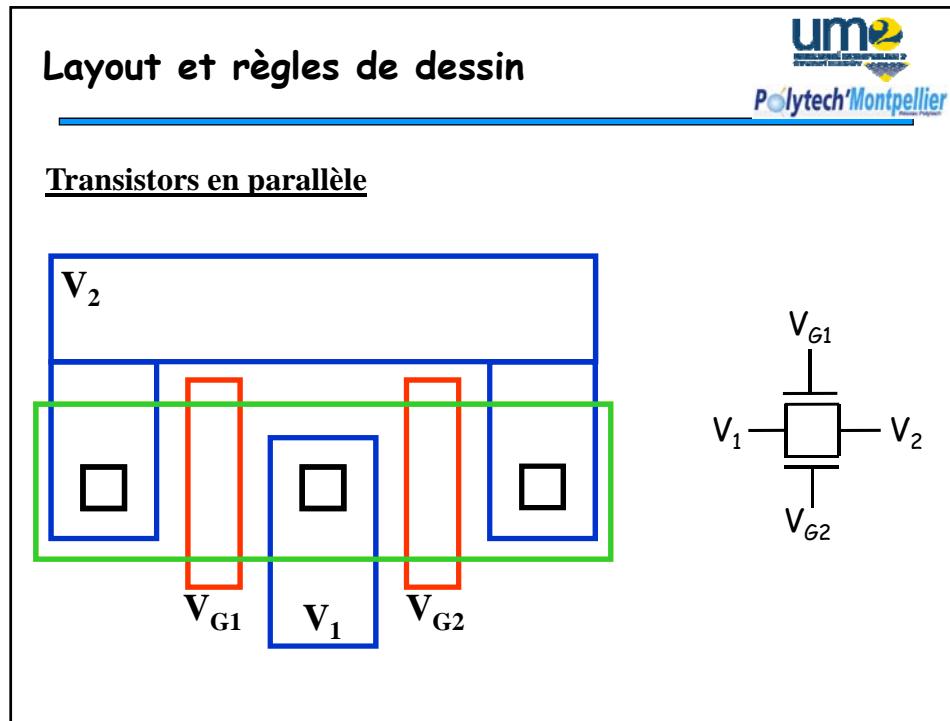

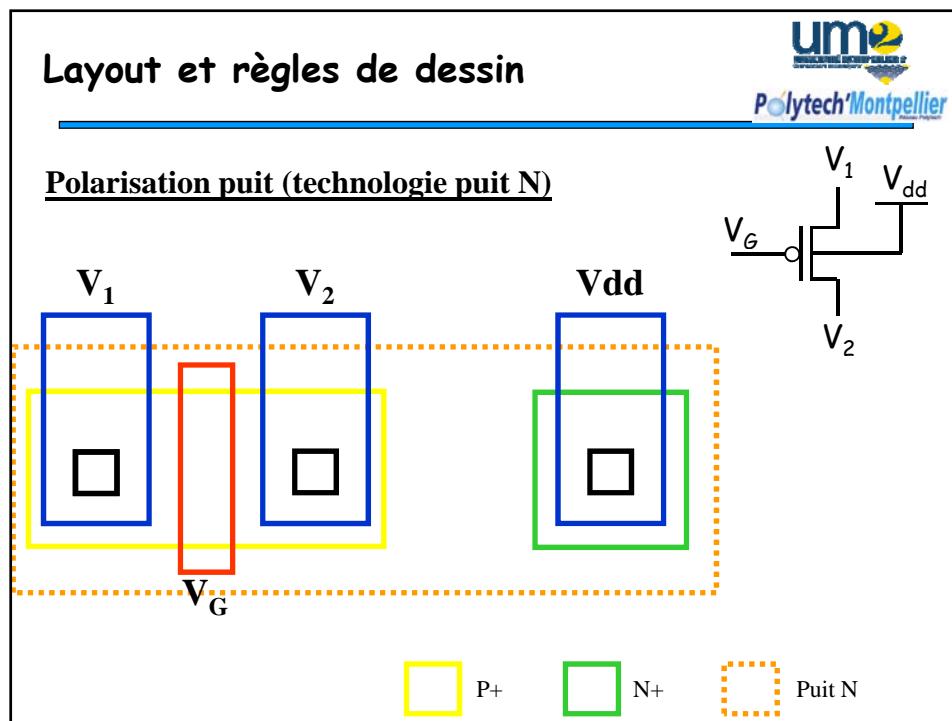

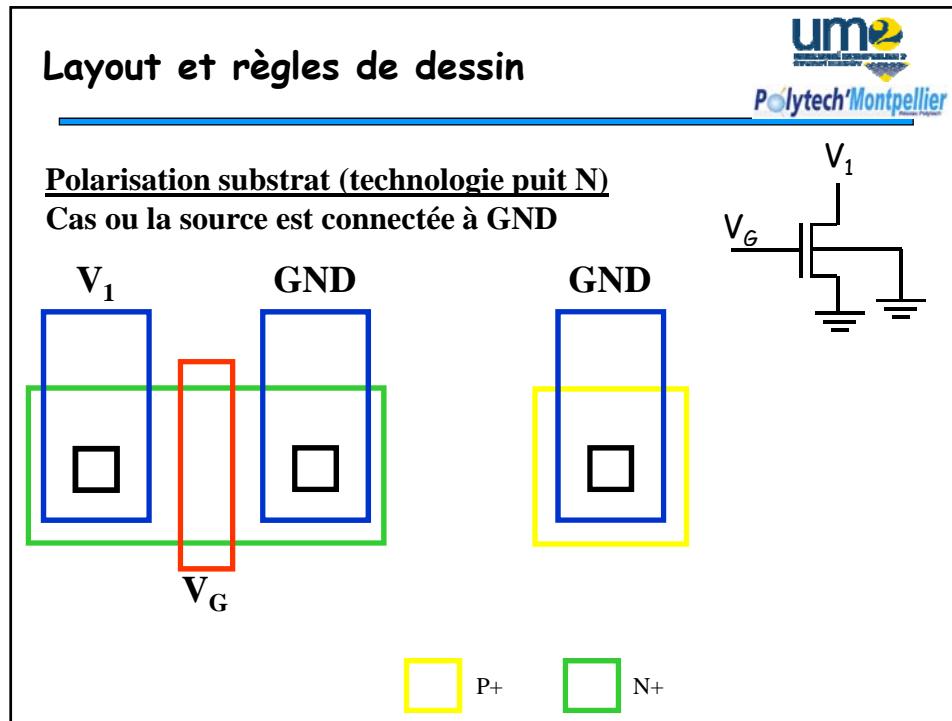

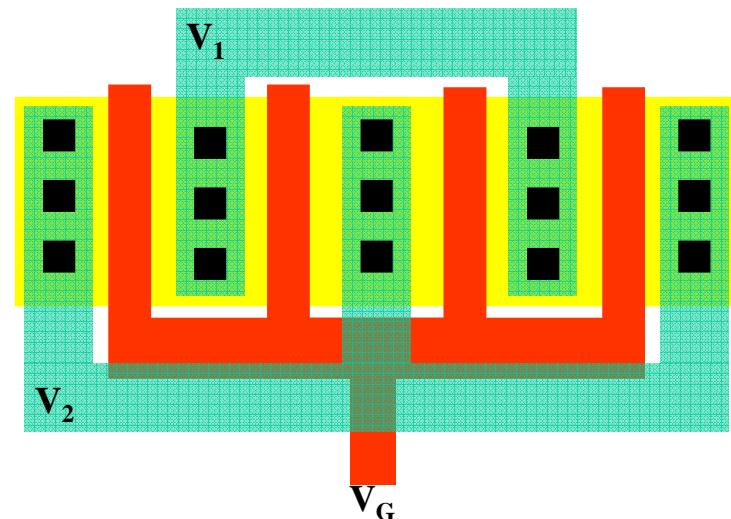

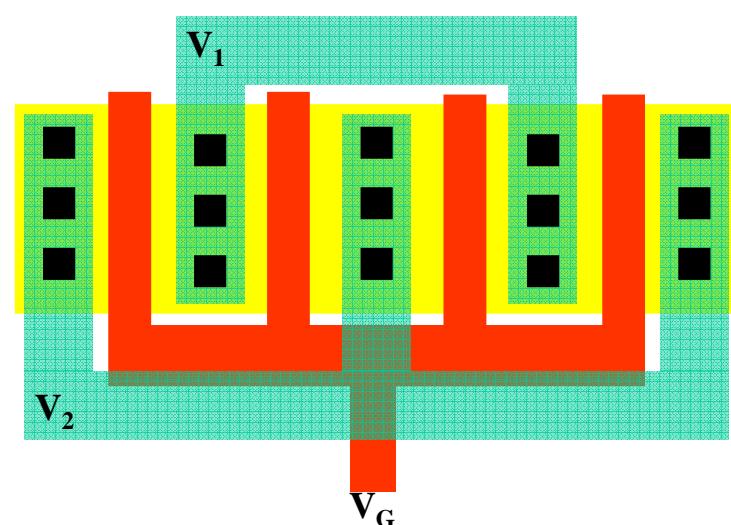

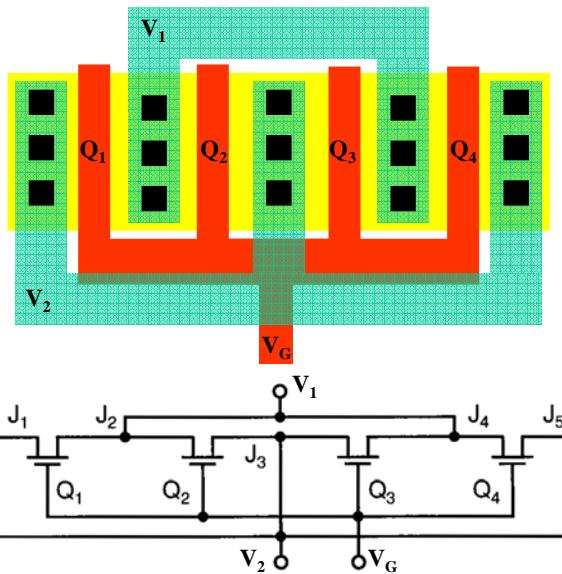

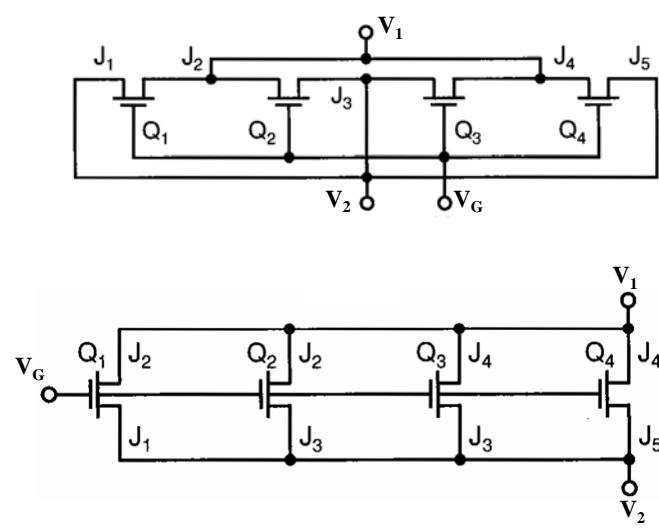

### Transistors en série

## Application : analyse de layout

N+

Poly

Contact

Métal

## Application : analyse de layout

N+

Poly

Contact

Métal

## Application : analyse de layout

## Application : analyse de layout

## Plan

- Introduction / généralités

- Procédé CMOS

- Layout et masques de fabrication

- Procédé CMOS et comportements parasites

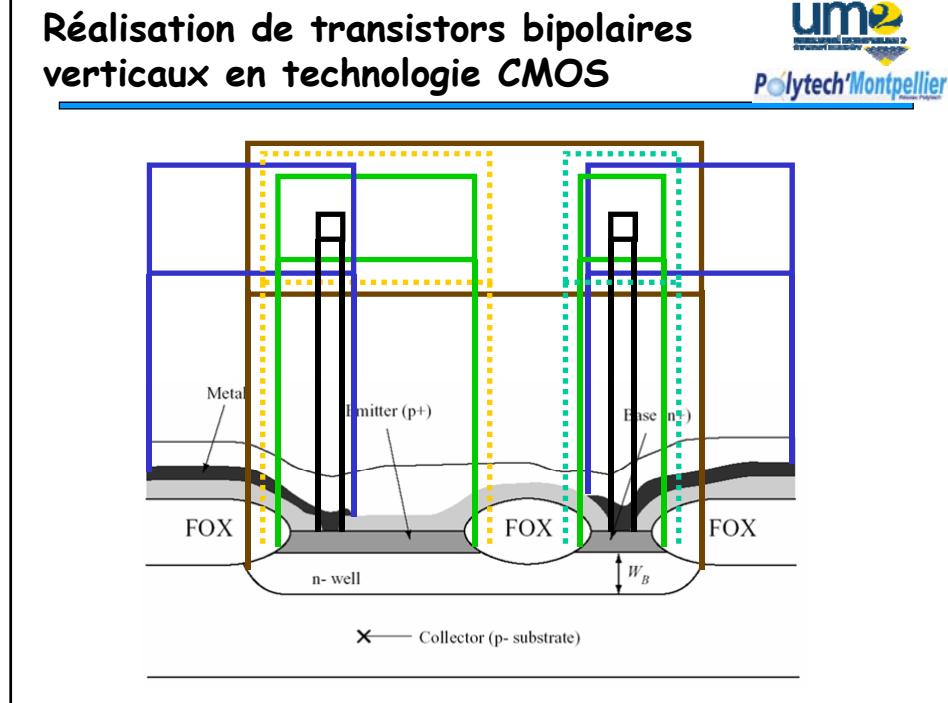

- Transistors bipolaires parasites et Latch-up

- Autres types d'agressions et Fiabilité

- Composants Passifs

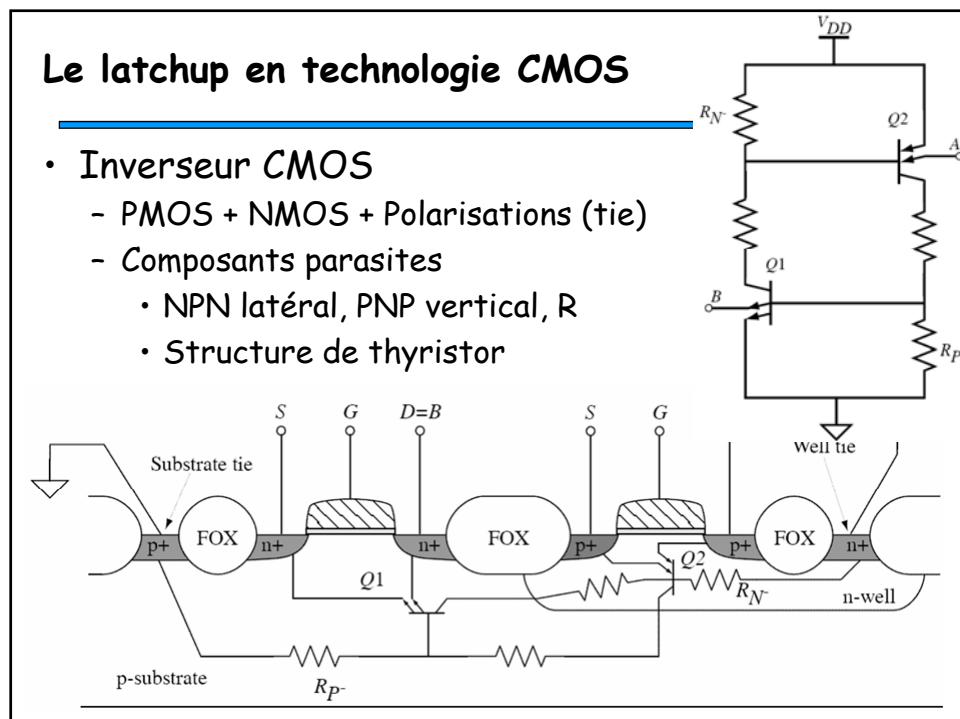

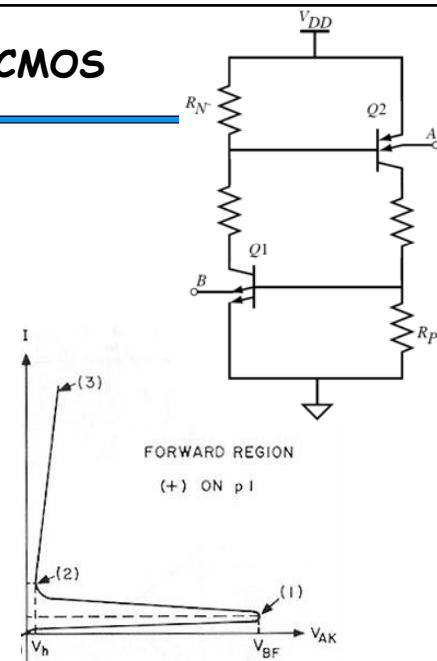

## Le latchup en technologie CMOS

- « accrochage »

- conduction en volume

- très faible résistance

- destruction thermique

## Les règles anti-latchup

- Réduire  $R_N$  et  $R_P$  ( $V_{be} \approx 0$ )

- Collecter les courants de fuite (puits - substrat)

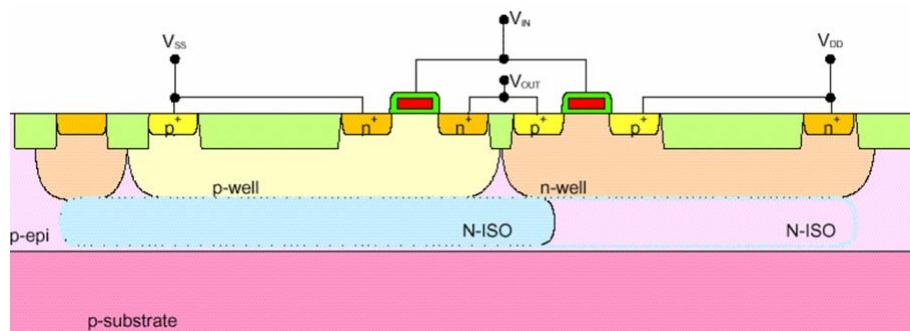

## Les règles anti-latchup

- Technologie double-puit (réduction de Rp)

- Utilisation de couches isolantes (N-ISO)

## Plan

- Introduction / généralités

- Procédé CMOS

- Layout et masques de fabrication

- Procédé CMOS et comportements parasites

- Transistors bipolaires parasites et Latch-up

- Autres types d'agressions et Fiabilité

- Composants Passifs

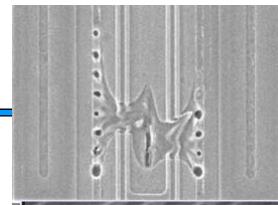

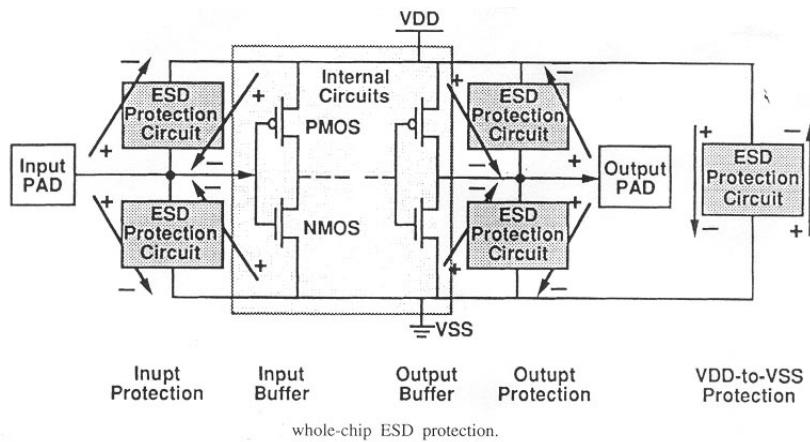

## Autres types d'agressions

- EMI/EOS/ESD

- deux plots chargés d'un circuit sont connectés

- un plot chargé est connecté à la masse

- Hard failures: fusion du silicium

- Soft failures:

- dégradation de  $V_t$ ,

- courants de fuite,

- défauts latents,

- vieillissement accéléré

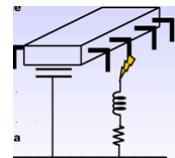

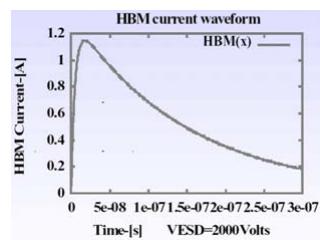

## Autres types d'agressions

- Trois types de décharge ESD

- Human Body Model (HBM)

- Machine Model (MM)

- Charged Device Model (CDM)

- Chaque standard est associé à :

- un circuit électrique

- Une procédure de test

- Un seuil de défaillance

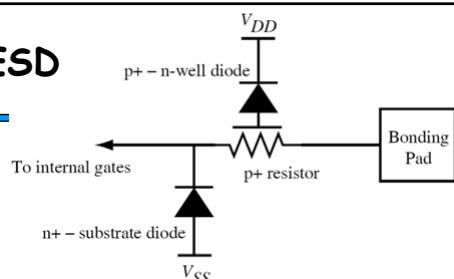

## La protection contre les ESD

## La protection contre les ESD

- Évacuer l'énergie en limitant la tension vue par les grilles de MOS

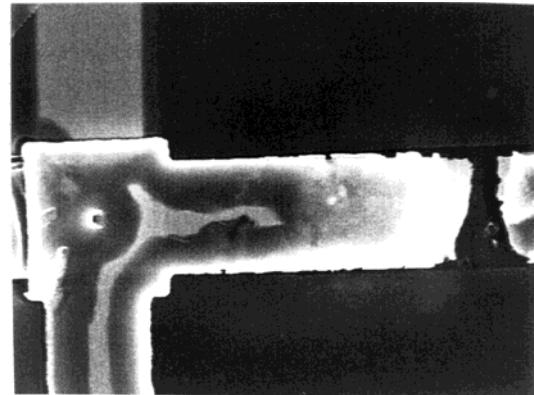

## Electromigration

**Limits dc-current to 1 mA/ $\mu\text{m}$**

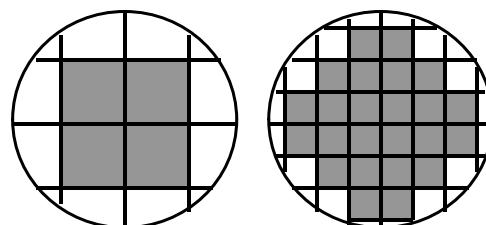

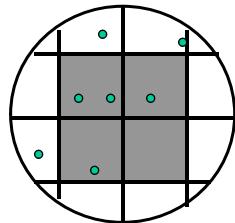

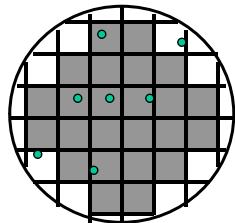

## Yield

$$Y = \frac{\text{No. of good chips per wafer}}{\text{Total number of chips per wafer}} \times 100\%$$

$$\text{Die cost} = \frac{\text{Wafer cost}}{\text{Dies per wafer} \times \text{Die yield}}$$

$$\text{Dies per wafer} = \frac{\pi \times (\text{wafer diameter}/2)^2}{\text{die area}} - \frac{\pi \times \text{wafer diameter}}{\sqrt{2} \times \text{die area}}$$

## Defects

Y=25%

Y=79%

$$\text{die yield} = \left( 1 + \frac{\text{defects per unit area} \times \text{die area}}{\alpha} \right)^{-\alpha}$$

$\alpha$  is approximately 3

$$\text{die cost} = f(\text{die area})^4$$

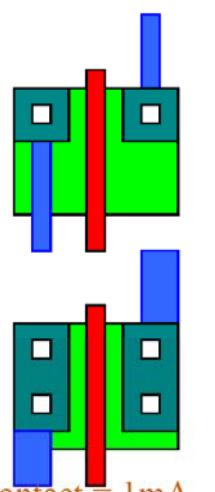

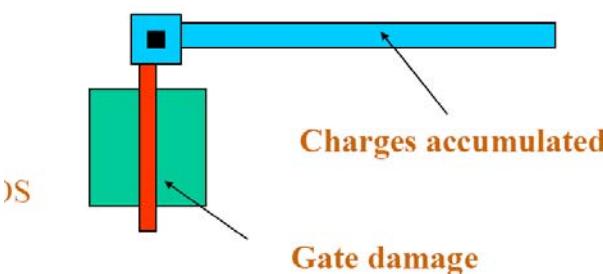

## Fiabilité et règles de dessin

## Fiabilité et règles de dessin

- 1 contact = 1mA

- Multiply contacts

$$\text{Antenna ratio} = \text{Area (metal)}/\text{Area(gate)}$$

Solution: Add diodes

## Plan

- Introduction / généralités

- Procédé CMOS

- Layout et masques de fabrication

- Procédé Bipolaire et BiCMOS

- Composants Passifs

- Capacités

- Résistances

- Packaging (boitier)

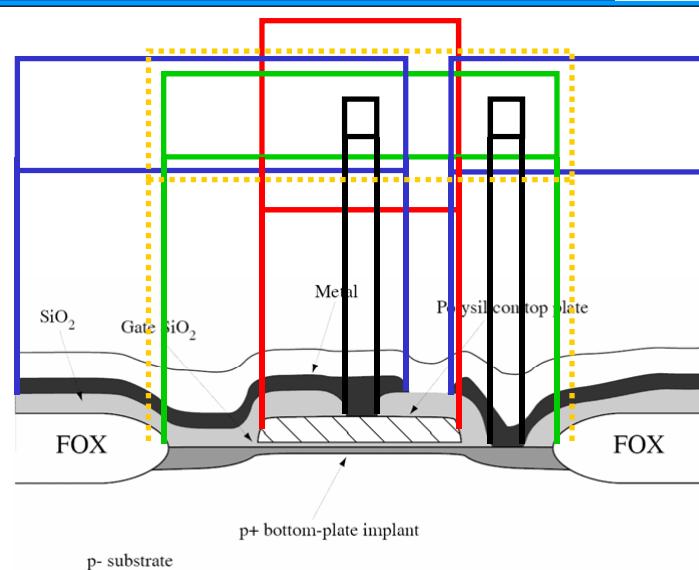

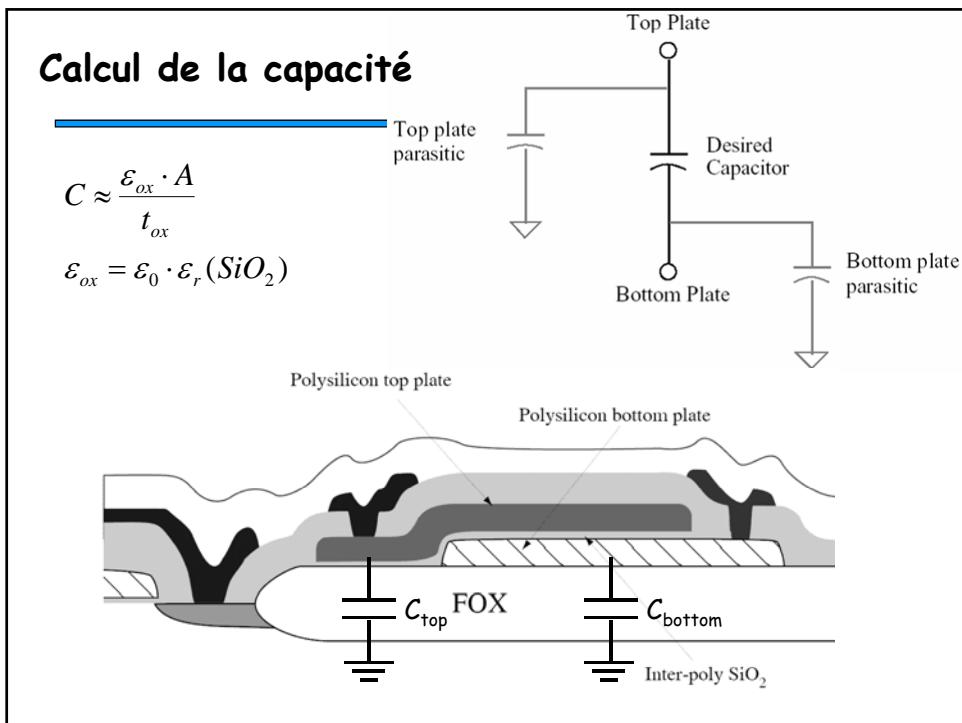

## Capacité de grille

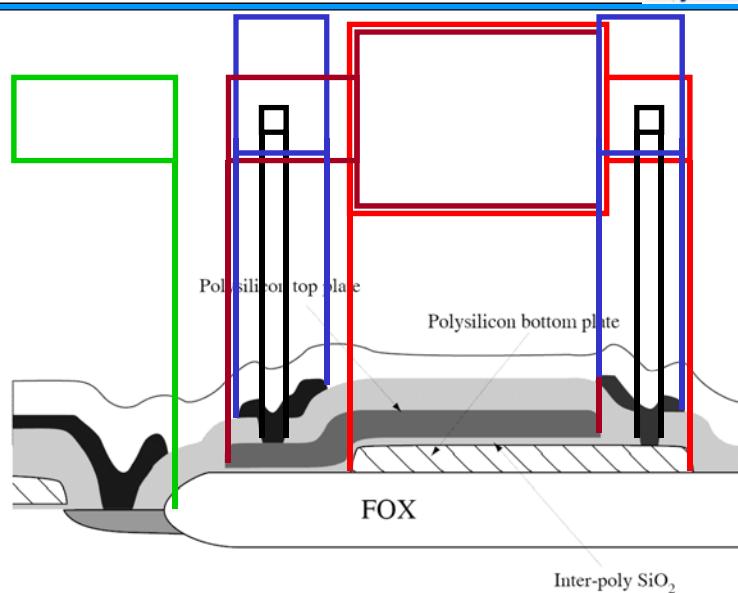

## Capacité poly-poly

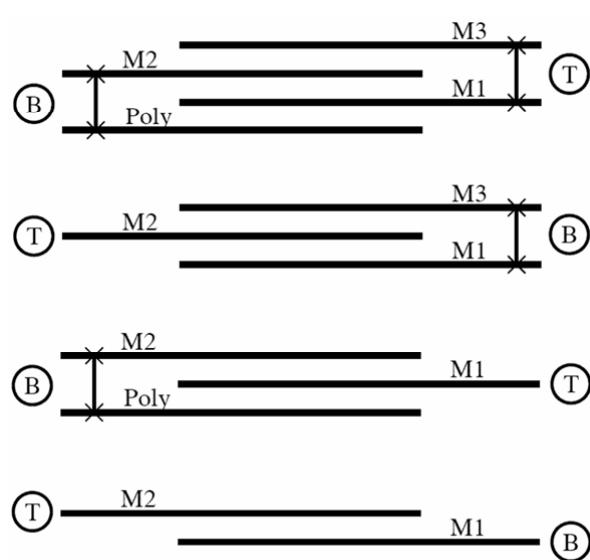

## Capacité Métal-Métal et Métal-Polysilicium

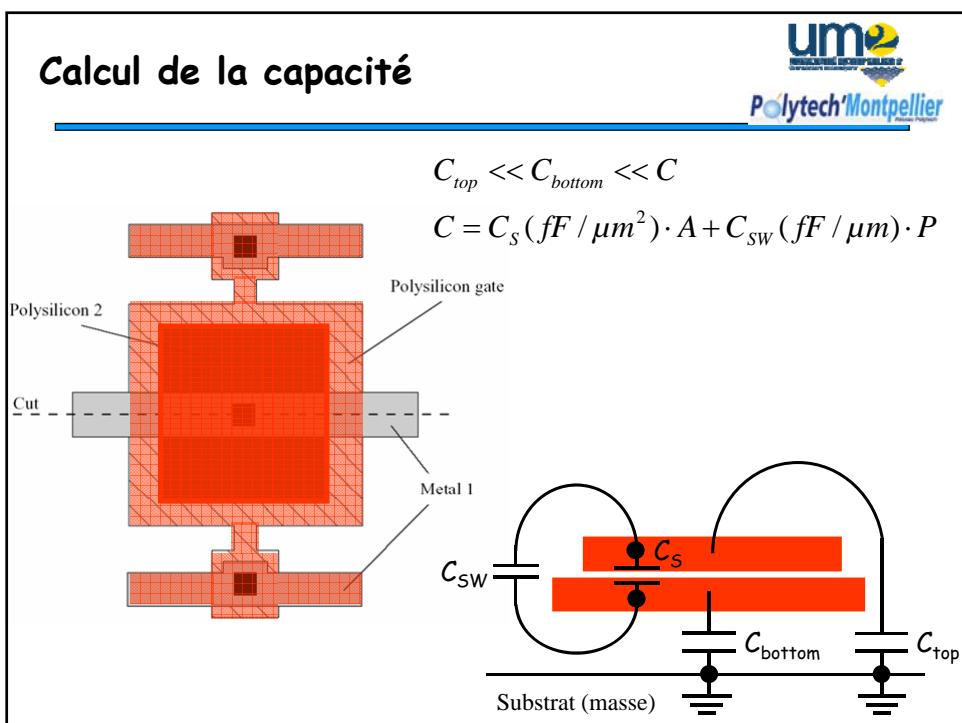

## Calcul de la capacité

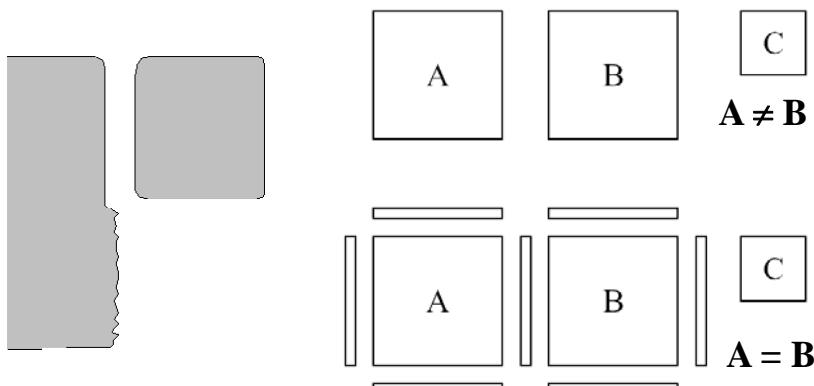

- Rapport  $C_2/C_1$  bien maîtrisé par conception

- $C_1 = C_s \cdot S_1 + C_{sw} \cdot P_1$  et  $C_2 = C_s \cdot S_2 + C_{sw} \cdot P_2$

- Avec contribution de périmètre négligeable

$$\frac{C_1}{C_2} = \frac{C_s S_1 + C_{sw} P_1}{C_s S_2 + C_{sw} P_2} = \frac{S_1}{S_2} \left[ \frac{1 + \frac{C_{sw} P_1}{C_s S_1}}{1 + \frac{C_{sw} P_2}{C_s S_2}} \right]$$

$$\frac{C_1}{C_2} \approx \frac{S_1}{S_2} \left[ 1 + \frac{C_{sw} P_1}{C_s S_1} - \frac{C_{sw} P_2}{C_s S_2} - \frac{C_{sw}^2 P_1 P_2}{C_s^2 S_1 S_2} \right] \quad \frac{C_1}{C_2} \approx \frac{S_1}{S_2} \left[ 1 + \frac{C_{sw}}{C_s} \left( \frac{P_1}{S_1} - \frac{P_2}{S_2} \right) \right]$$

Le meilleur appariement sera obtenu pour des rapports périmètre à surface identiques

## Prise en compte des problèmes liés à la gravure

- Problèmes liés aux grandes dimensions, aux structures isolées (voisinage)

## Prise en compte des problèmes liés à la gravure

- Sous- et sur-gravures dans les angles

- Présence de gradients

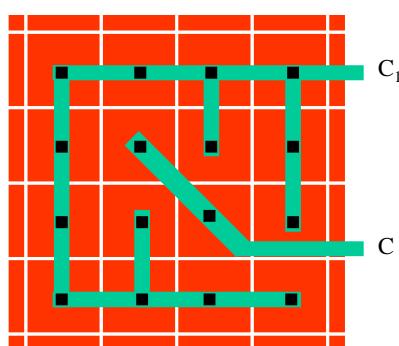

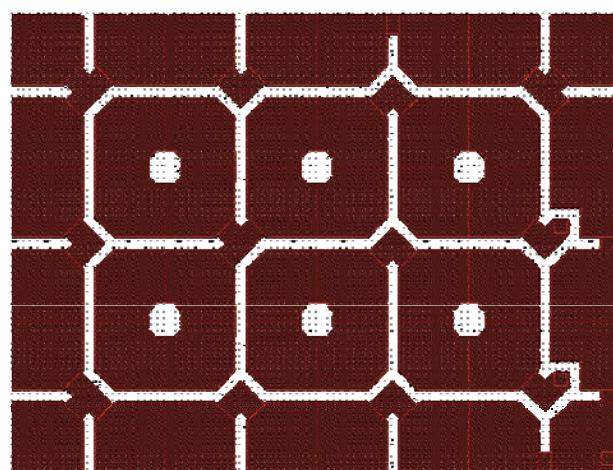

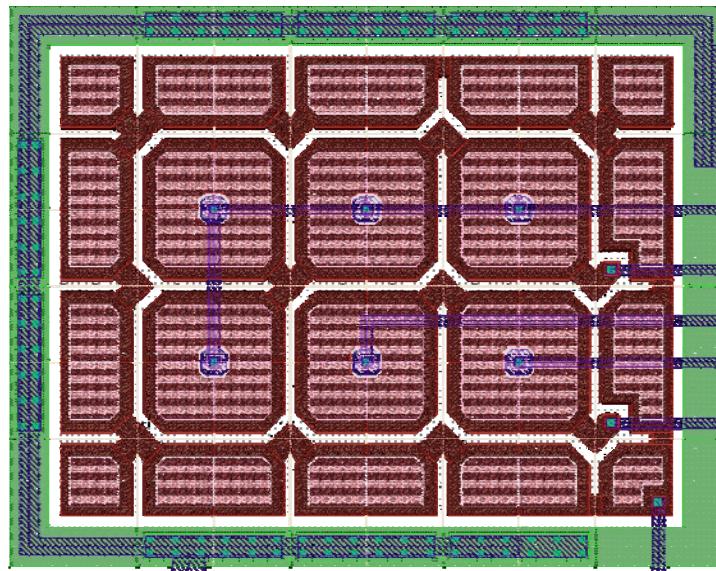

## Mise en œuvre (1/4)

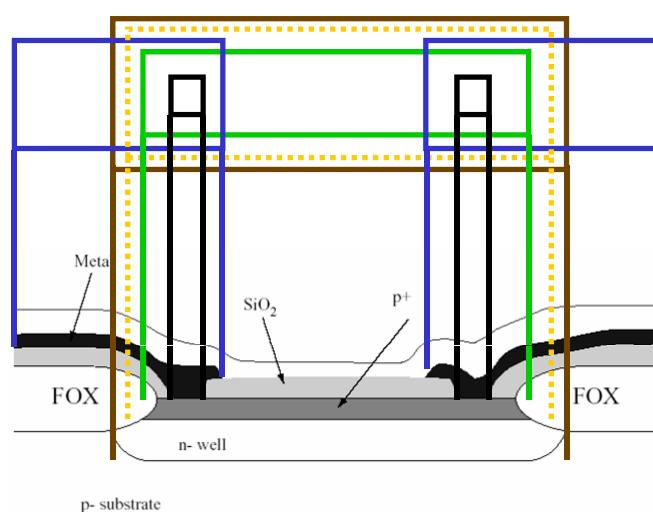

- Capacités intégrées : 2 électrodes en polysilicium avec un isolant très mince (qq 10nm)

- $C = C_s \cdot S + C_{sw} \cdot P$  (avec  $C_s$  de l'ordre de  $1fF/\mu m^2$ )

- Vue en coupe

- Capa unitaire ( $\approx 10\mu m^2$ ) de valeur absolue imprécise

- Rapports de capacités (ex :  $C_1/C=7$ )

- Structure centroïde

## Mise en œuvre (2/4)

## Mise en œuvre (3/4)

## Mise en œuvre (4/4)

## Plan

- Introduction / généralités

- Procédé CMOS

- Layout et masques de fabrication

- Procédé Bipolaire et BiCMOS

- Composants Passifs

- Capacités

- Résistances

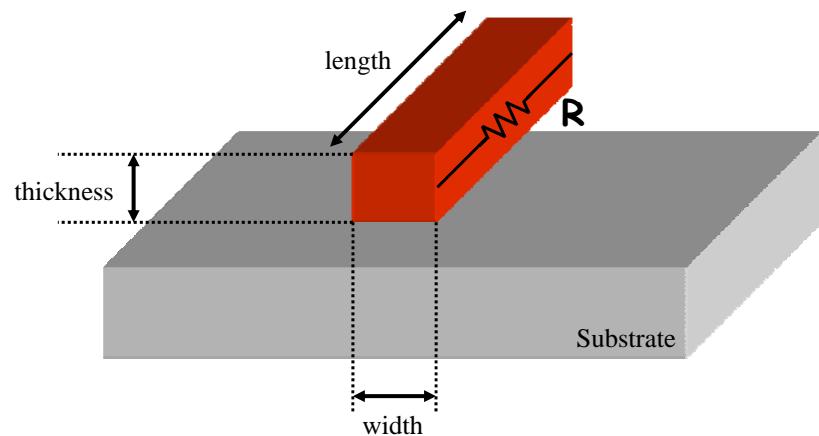

## Resistance calculation

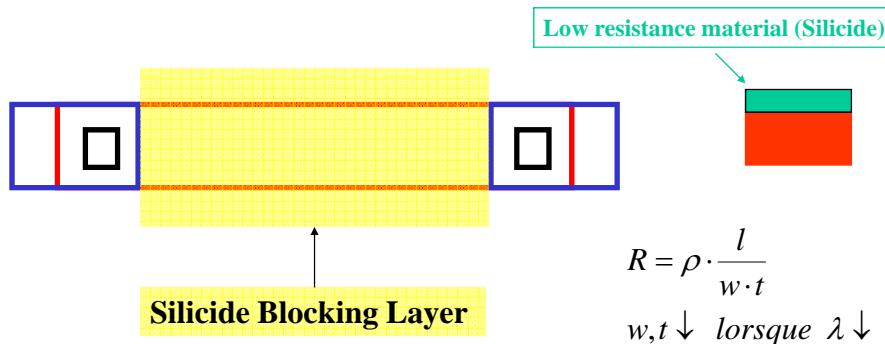

$$R = \rho \cdot \frac{l}{w \cdot t} \Rightarrow R = \frac{\rho}{t} \cdot \frac{l}{w} \Rightarrow R = R \cdot \frac{l}{w}$$

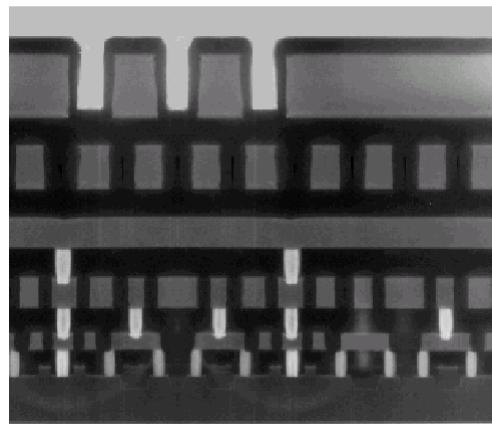

## Polycide Gate MOSFET

Silicides: WSi<sub>2</sub>, TiSi<sub>2</sub>, PtSi<sub>2</sub> and TaSi

Conductivity: 8-10 times better than Poly

## Interconnect Resistance

| Material      | $\rho$ ( $\Omega\text{-m}$ ) |

|---------------|------------------------------|

| Silver (Ag)   | $1.6 \times 10^{-8}$         |

| Copper (Cu)   | $1.7 \times 10^{-8}$         |

| Gold (Au)     | $2.2 \times 10^{-8}$         |

| Aluminum (Al) | $2.7 \times 10^{-8}$         |

| Tungsten (W)  | $5.5 \times 10^{-8}$         |

## Sheet Resistance

| Material                             | Sheet Resistance ( $\Omega/\square$ ) |

|--------------------------------------|---------------------------------------|

| n- or p-well diffusion               | 1000 – 1500                           |

| $n^+, p^+$ diffusion                 | 50 – 150                              |

| $n^+, p^+$ diffusion with silicide   | 3 – 5                                 |

| $n^+, p^+$ polysilicon               | 150 – 200                             |

| $n^+, p^+$ polysilicon with silicide | 4 – 5                                 |

| Aluminum                             | 0.05 – 0.1                            |

## Example: Intel 0.25 micron Process

5 metal layers

Ti/Al - Cu/Ti/TiN

| LAYER       | PITCH | THICK | A.R. |

|-------------|-------|-------|------|

| Isolation   | 0.67  | 0.40  | -    |

| Polysilicon | 0.64  | 0.25  | -    |

| Metal 1     | 0.64  | 0.48  | 1.5  |

| Metal 2     | 0.93  | 0.90  | 1.9  |

| Metal 3     | 0.93  | 0.90  | 1.9  |

| Metal 4     | 1.60  | 1.33  | 1.7  |

| Metal 5     | 2.56  | 1.90  | 1.5  |

|             | μm    | μm    |      |

Layer pitch, thickness and aspect ratio

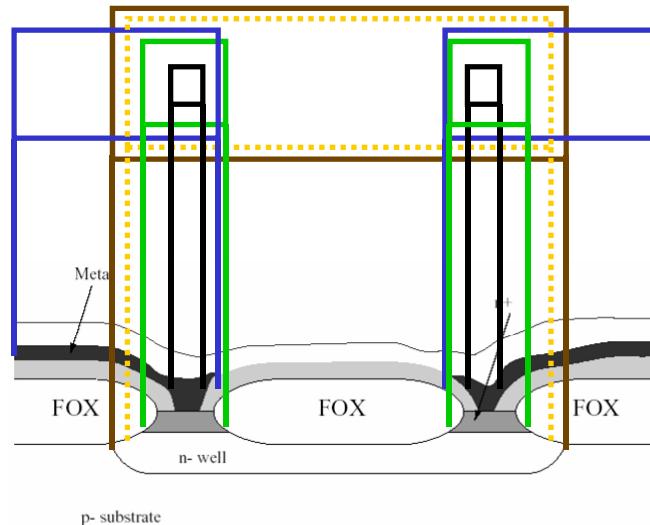

## Résistance Polysilicium (1/4)

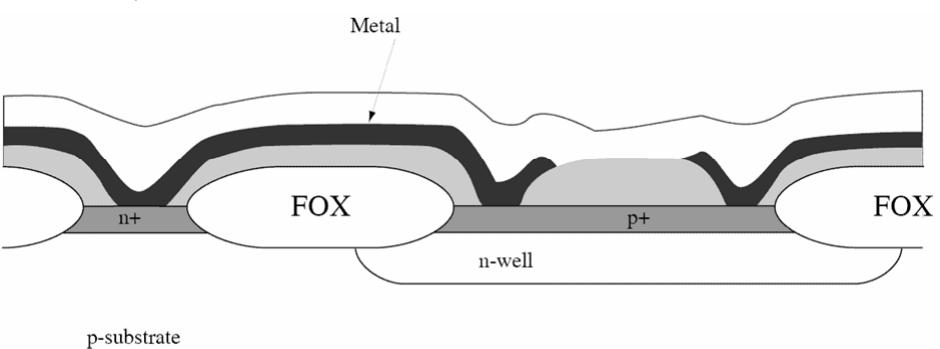

p- substrate

## Résistance Polysilicium (2/4)

## Résistance Polysilicium (3/4)

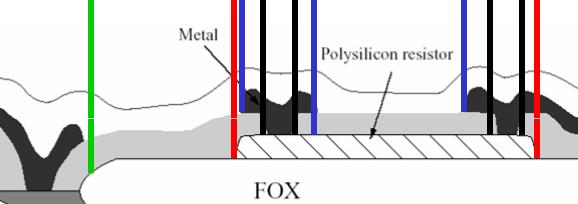

- Résistances intégrées : silicium polycristallin

- $R=N_{\square} \times R_{\square}$  (avec  $R_{\square}$  de l'ordre de 20-200  $\Omega$ )

- Incertitudes fortes sur la valeur absolue

- Bonne précision sur la valeur relative

- Poly HR (Analog) :  $\times 1000$

- Silicided Polysilicon (Digital) :  $/ 10$

## Résistance Polysilicium (4/4)

## Autres résistances : diffusée

## Autres résistances : N-Well

## Composants passifs: performances typiques (CMOS 0.8 μm)

| Component Type      | Range of Values               | Matching Accuracy | Temperature Coefficient | Voltage Coefficient | Absolute Accuracy |

|---------------------|-------------------------------|-------------------|-------------------------|---------------------|-------------------|

| Poly/poly capacitor | 0.8-1.0 fF/ $\mu\text{m}^2$   | 0.05%             | 50 ppm/°C               | 50 ppm/V            | ±10%              |

| MOS capacitor       | 2.2-2.5 fF/ $\mu\text{m}^2$   | 0.05%             | 50 ppm/°C               | 50 ppm/V            | ±10%              |

| MOM capacitor       | 0.02-0.03 fF/ $\mu\text{m}^2$ | 1.5%              |                         |                     | ±10%              |

| Diffused resistor   | 20-150 $\Omega/\text{sq.}$    | 0.4%              | 1500 ppm/°C             | 200 ppm/V           | ±35%              |

| Polysilicide R      | 2-15 $\Omega/\text{sq.}$      |                   |                         |                     |                   |

| Poly resistor       | 20-40 $\Omega/\text{sq.}$     | 0.4%              | 1500 ppm/°C             | 100 ppm/V           | ±30%              |

| N-well resistor     | 1-2k $\Omega/\text{sq.}$      | 0.4%              | 8000 ppm/°C             | 10k ppm/V           | ±40%              |

## Plan

- Introduction / généralités

- Procédé CMOS

- Layout et masques de fabrication

- Procédé Bipolaire et BiCMOS

- Composants Passifs

- Capacités

- Résistances

- Packaging (boitier)

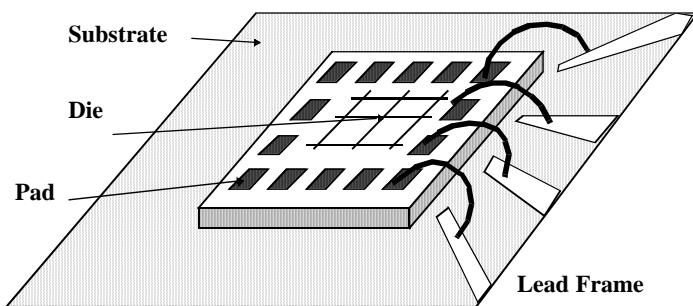

## Mise en boitier

### Packaging

#### Requirements

- Electrical: Low parasitics

- Mechanical: Reliable and Robust

- Thermal: Efficient Heat Removal

- Economical: Cheap

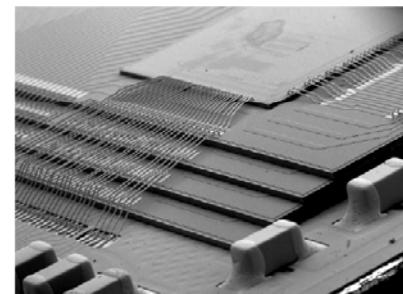

## Bonding Techniques

### Wire Bonding

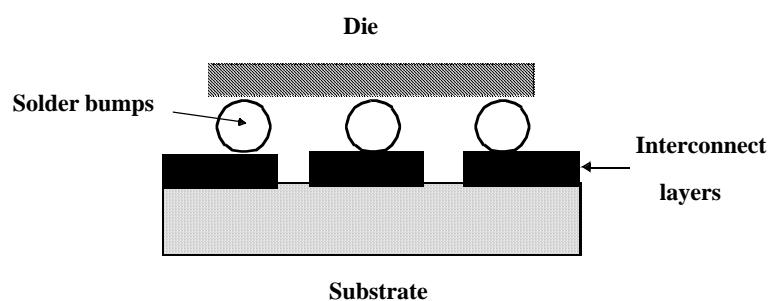

## Flip-Chip Bonding

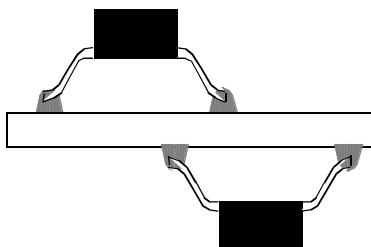

## Package-to-Board Interconnect

(a) Through-Hole Mounting

(b) Surface Mount

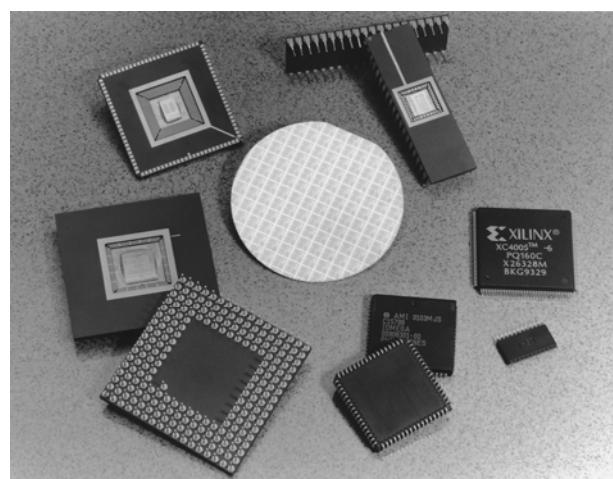

## Package Types

## Package Parameters

| Package Type           | Capacitance (pF) | Inductance (nH) |

|------------------------|------------------|-----------------|

| 68 Pin Plastic DIP     | 4                | 35              |

| 68 Pin Ceramic DIP     | 7                | 20              |

| 256 Pin Pin Grid Array | 5                | 15              |

| Wire Bond              | 1                | 1               |

| Solder Bump            | 0.5              | 0.1             |

Typical Capacitances and Inductances of Various Package and Bonding Styles (from [Sze83])

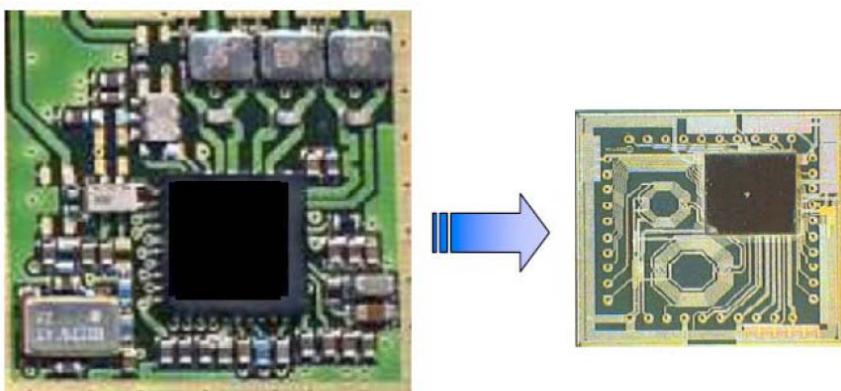

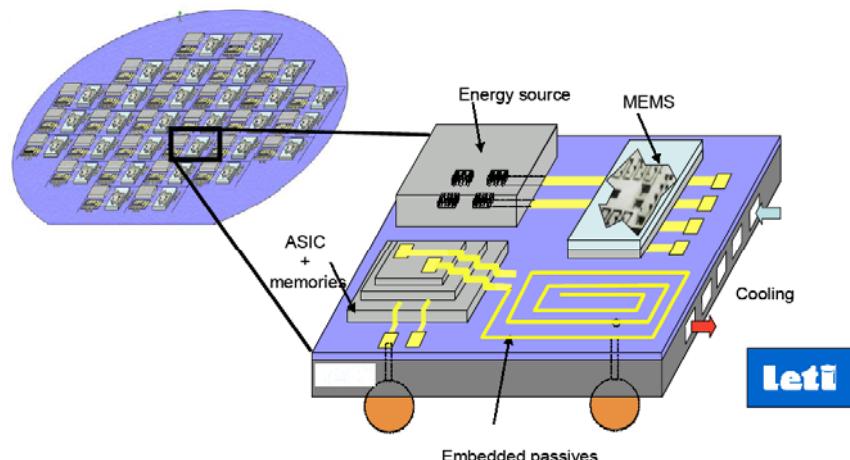

## Advanced packaging techniques

- System in Package

- Smaller, better, cheaper

## Advanced packaging techniques

- Wafer Level SiP

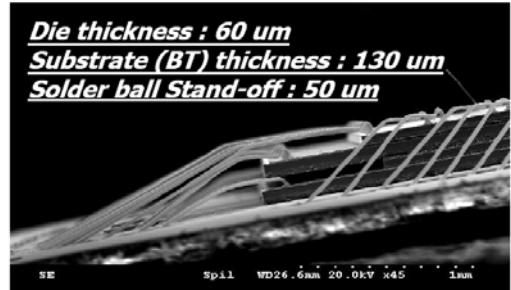

## Advanced packaging techniques

- Die stacking for SiP

**SPIL**

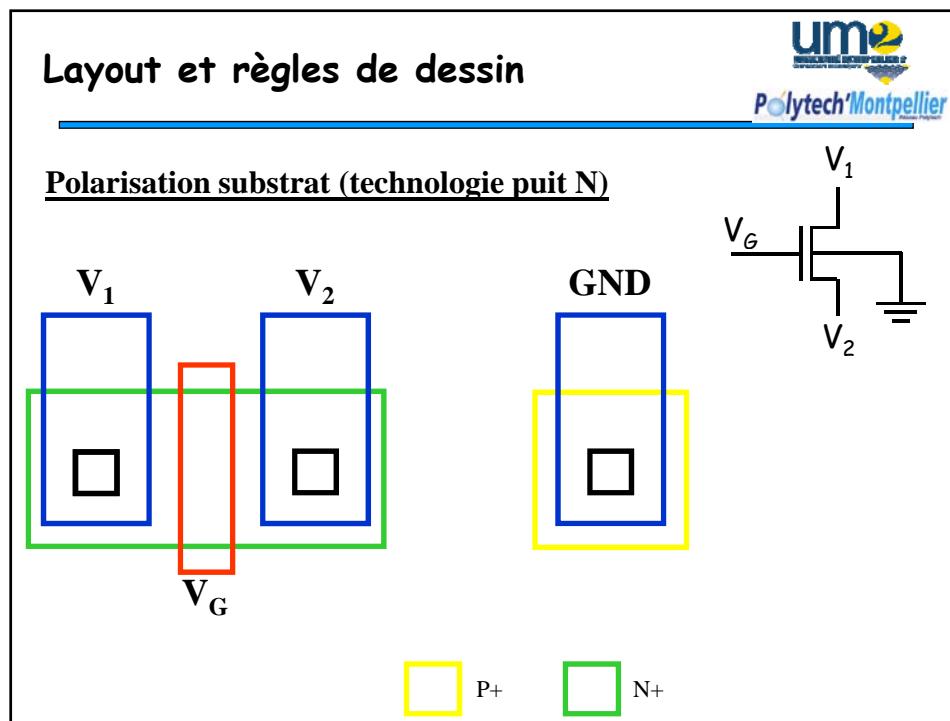

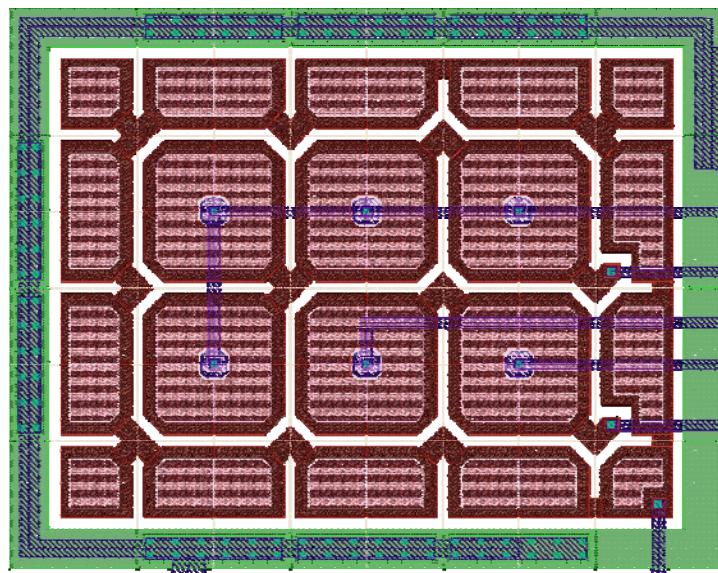

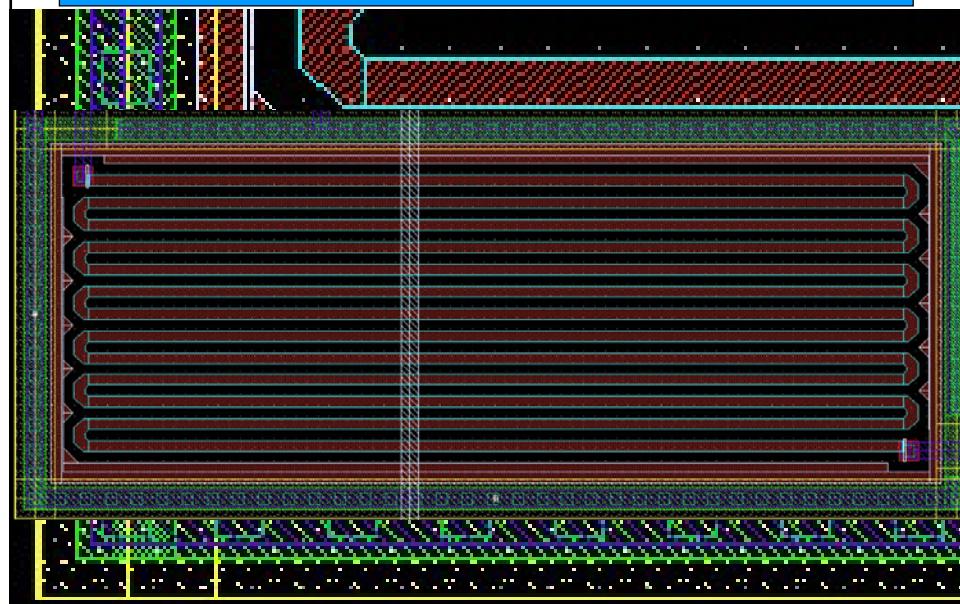

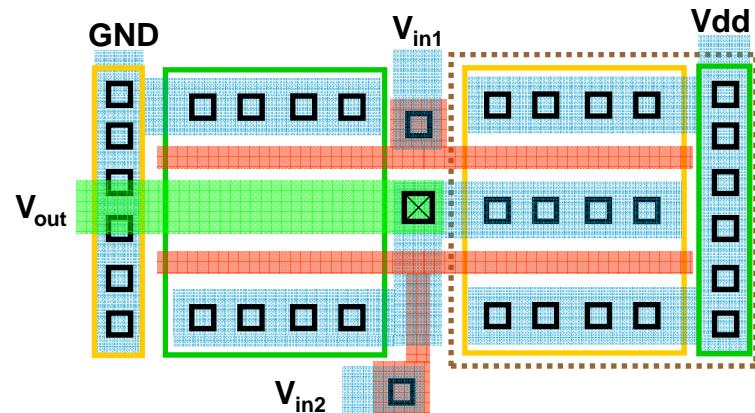

**Exercice n°1**

□ Puit N   □ P+   □ N+   ■ Polysilicium

■ M1   ■ M2   □ Contact   ☒ Via M1-M2

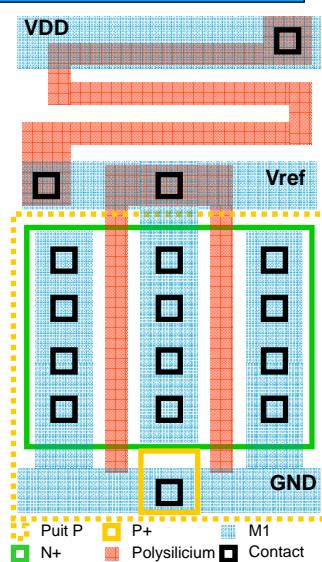

**Exercice n°2**

- a) Analysez le layout de la figure ci-contre et donnez le schéma électrique réalisé en précisant le W/L des transistors.

On donne  $R_{poly} = 30 \Omega/\square$

## Références

- [www.youtube.com](http://www.youtube.com)

- Allen and Holberg

« CMOS Analog Circuit Design »

- J. M. Rabaey and al.,

« Digital Integrated Circuits », Prentice-Hall.

- [www.inemi.org](http://www.inemi.org) ; [www.amd.com](http://www.amd.com) ; [www.intel.com](http://www.intel.com)

- Applets Java pour la fabrication d'un inverseur

<http://jas.eng.buffalo.edu/education/fab/invFab/>

- Remerciements : Michel Renovell

« CAO des Circuits Intégrés » - Cours M1 EEA

Université Montpellier II

## Résumé

- Masque