|

| |

|

| |

| |

|

| |

| |

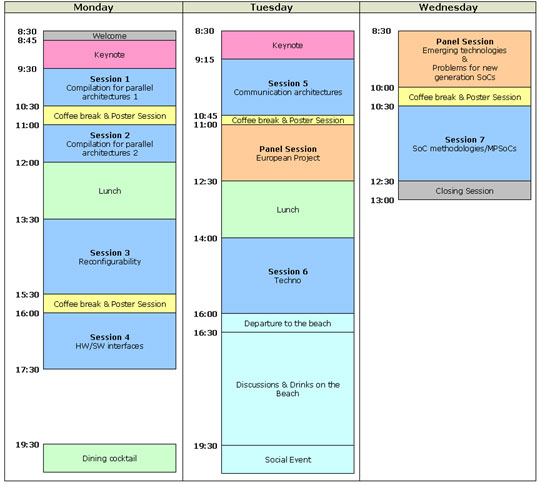

| Monday June 27 |

| |

| 8:30-8:45 |

Welcome |

| 8:45- 9:30 |

Keynote

Embedded Test and Diagnosis

Hans Joachim Wunderlich

Institut für Technische Informatik, University of Stuttgart, Germany |

| 9:30-10:30 |

Session 1 : Compilation for parallel

architectures 1

Session Chair : Alfredo Rosado |

| |

9:30-10:00 |

High-Level-Language Compilation for Reconfigurable

Computers

Andreas Koch

Embedded Systems and Applications Group, Darmstadt University of Technology, Germany |

| |

10:00-10:30 |

Symbiotic Processing: Toward a Better Balance Between Architecture, Compiler and User Efforts

Yves Lhuillier

LRI, Paris South University & INRIA Futurs, France |

| 10:30-11:00 |

Coffee Break & Poster Session |

| 11:00-12:00 |

Session 2 : Compilation for parallel

architectures 2

Session Chair : Andreas Koch |

| |

11:00-11:30 |

Compiler level integration of a portable CAD

framework for reconfigurable circuits

Bernard Pottier

Universite de Bretagne Occidentale, France |

| |

11:30-12:00 |

Co-Design of Massively Parallel Embedded Processor

Architectures

Hritam Dutta

Department of Computer Science, Hardware-Software-Co-Design,University of Erlangen-Nuremberg, Germany |

| 12:00-13:30 |

Lunch |

| 13:30-15:30 |

Session 3 : Reconfigurability

Session Chair : Gilles Sassatelli |

| |

13:30-14:00 |

Dynamic Reconfiguration On-Demand: Real-time

Adaptivity in Next Generation Microelectronics

Juergen Becker, Institut für Technik der Informationsverarbeitung (ITIV), University of Karlsruhe, Germany |

| |

14:00-14:30 |

An adaptive FPGA and its distributed routing

Yann Thoma

Ecole Polytechnique Federale de Lausanne, Switzerland |

| |

14:30-15:00 |

Analysis and Architectural Study of a Hybrid ASIC/Configurable State Machine Model

Peter Zipf

Institute of Microelectronic Systems, Darmstadt University of Technology, Germany |

| |

15:00-15:30 |

Implementation of Scalabale Embedded FPGA for SOC

Hayder Mrabet

LIP6-ASIM Laboratory, University of Paris 6, France |

| 15:30-16:00 |

Coffee Break & Poster Session |

| 16:00-17:30 |

Session 4 : HW/SW interfaces

Session Chair : Thomas Hollstein |

| |

16:00-16:30 |

Feedback control modelling of learning reconfigurable

embedded systems

Jean-Philippe Diguet

LESTER, CNRS / UBS Research center, Lorient, France |

| |

16:30-17:00 |

Exploring RTOS issues with a high-level model

of a reconfigurable SoC platform

François Verdier

ETIS, ENSEA / Université de Cergy-Pontoise, France |

| |

17:00-17:30 |

Experiences on actor-oriented design of reconfigurable and communication-centric systems

Leandro Soares Indrusiak

Institute of Microelectronic Systems, Darmstadt University of Technology, Germany |

| 19:30 |

Dining cocktail |

| |

|

|

| Tuesday June 28 |

| |

| 8:30-9:15 |

Keynote

Implementation Trade-Offs of Advanced Channel Decoding Algorithms for 3/4G Communication System

Norbert Wehn

Microelectronic System Design Research Group, University of Kaiserslautern, Germany |

| 9:15-10:45 |

Session 5 : Communication architectures

Session Chair : Juergen Becker |

| |

9:15-9:45 |

Advanced On-Chip Communication Architectures and Routing Methods for Systems-on-Chip

Thomas Hollstein

Institute of Microelectronic Systems, Darmstadt University of Technology, Germany |

| |

9:45-10:15 |

Proposition of a benchmark for evaluation of cores mapping onto NoC architectures

Dominique Houzet

INSA/ IETR Laboratory, Rennes / CEA-LETI, Grenoble, France |

| |

10:15-10:45 |

System Monitoring and Reconfiguration in Proteo

NoC

David Sigüenza-Tortosa

Tampere University of Technology, Finland |

| 10:45-11:00 |

Coffee Break & Poster Session |

| 11:00-12:30 |

Panel Session : European Projects |

| 12:30-14:00 |

Lunch |

| 14:00-16:00 |

Session 6 : Techno

Session Chair : Peter Zipf |

| |

14:00-14:30 |

Flash challenges

Jean Michel Daga

ATMEL, Rousset, France |

| |

14:30-15:00 |

Asynchronous Systems on Programmable Logic

Marc Renaudin

TIMA Laboratory, Grenoble, France |

| |

15:00-15:30 |

Non-volatil FPGA based on Magnetic Tunneling

Junction

Nicolas Bruchon

LIRMM, CNRS/University of Montpellier 2, Montpellier, France |

| |

15:30-16:00 |

Towards reconfigurable optical networks on

chip

Ian O'connor

LEOM, Ecole Centrale de Lyon, Ecully, France |

| 16:00-16:30 |

Departure to the beach |

| 16:30-19:30 |

Discussions & drinks on the beach |

| 19:30 |

Social Event |

| |

|

|

| Wednesday June 29 |

| |

| 8:30-10:00 |

Panel Session : Emerging

technologies & problems for new generation SoCs |

| 10:00-10:30 |

Coffee Break & Poster Session |

| 10:30-12:30 |

Session 7 : SoC methodologies

Session Chair : Leandro Soares Indrusiak |

| |

10:30-11:00 |

Model Driven Engineering for Regular MPSOC Co-design

Jean-Luc Dekeyser

Laboratoire dInformatique Fondamentale de Lille, Lille, France |

| |

11:00-11:30 |

Power/Energy Estimation in SoCs by Multi-Level

Parametric Modeling

Nathalie Julien, LESTER, CNRS / UBS Research center, Lorient, France |

| |

11:30-12:00 |

Formal methods for Embedded Systems Co-design:the

FORDESIGN project

Luis Gomes

Universidade Nova de Lisboa, Faculty of Sciences and Technology, Dep. of Electrical Engineering & UNINOVA, Portugal |

| |

12:00-12:30 |

Design and Implementation of a Multi-Core Architecture

for Overhead Processing in Optical Transport Networks

Tudor Murgan

Institute of Microelectronic Systems, Darmstadt University of Technology, Germany |

| 12:30-13:00 |

Closing session |

| |

|

|

|

| |

|