|

|

|

|

|

|

| |

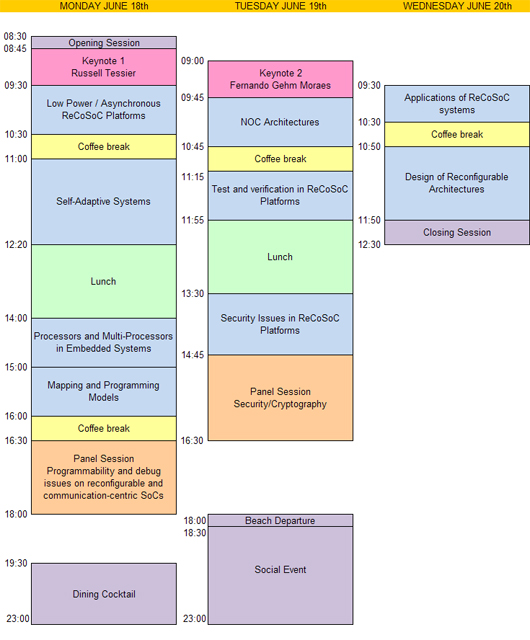

| Monday June 18th |

| |

8:30-8:45

|

Opening

Session |

8:45-

9:30

|

Keynote

1

Power-reduction Techniques for Reconfigurable Communication-Centric

SoCs: Technologies and Trends

Russell Tessier

Chair : Leandro Soares Indrusiak

|

| 9:30-10:30 |

Session

1: Low Power / Asynchronous ReCoSoC Platforms

Session Chair: Peter Zipf |

| |

9:30-9:50 |

Exploitation of Run-Time

Partial Reconfiguration for Dynamic Power. Management

in Xilinx Spartan III-based Systems

Katarina Paulsson, Michael Hübner, Salih Bayar,

Jürgen Becker

Universität Karlsruhe (TH), Germany

|

| |

9:50-10:10 |

Low-Complexity Adaptive Encoding

Schemes Based on Partial Bus-Invert for Power Reduction

in Buses Exhibiting Capacitive Coupling

T.Murgan, A.Guntoro, H.Hinkelmann, P. B. Bacinschi,

and M.Glesner

Darmstadt University of Technology – Institute

of Microelectronic Systems, Germany

|

|

10:10-10:30 |

A Reconfigurable Cell for a Multi-Style Asynchronous

FPGA

Philippe Hoogvorst, Sylvain Guilley,

Sumanta Chau Alin Razafindraibe, Taha Beyrouthy, Laurent

Fesquet

ENST Paris / TIMA, Grenoble, France |

| 10:30-11:00 |

Coffee Break |

| 11:00-12:20 |

Session 2: Self-Adaptive

Systems

Session Chair: Michael Huebner |

| |

11:00-11:20 |

A NoC-based Infrastructure

to Enable Dynamic Self Reconfigurable Systems

Leandro Möller, Ismael Grehs, Ewerson Carvalho,

Rafael Soares, Ney Calazans, Fernando Moraes

Darmstadt University of Technology – Institute

of Microelectronic Systems, Germany

Catholic University of

Rio Grande do Sul (FACIN-PUCRS), Brazil

|

| |

11:20-11:40 |

Dynamic Relocation of Hybrid

Tasks: A Complete Design Flow

Marcelo Götz, Tao Xie, Florian

Dittmann

University of Paderborn, Germany

|

| |

11:40-12:00

| HS Scale: A run-time adaptable

MP-SoC architecture

Nicolas Saint-Jean, Camille Jalier, Gilles Sassatelli,

Pascal Benoit, Lionel Torres, Michel Robert

LIRMM - CNRS, University of Montpellier 2, France

|

|

12:00-12:20

| System Level Design of a

Dynamically Self-Reconfigurable Image Processing System

Kurt Franz Ackermann, Leandro Soares Indrusiak,

Manfred Glesner

Institute for Microelectronic Systems, Technische Universität

Darmstadt, Vitronic GmbH, Germany |

| 12:20-14:00 |

Lunch |

| 14:00-15:00 |

Session 3: Processors and

Multi-Processors in Embedded Systems

Session Chair: Michel Paindavoine |

|

14:00-14:20 |

A Customizable LEON2-Based

VLIW Processor

Peter Zipf, Heiko Hinkelmann, Felix Missel,

Manfred Glesner

Institute of Microelectronic Systems Darmstadt University

of Technology, Germany

|

| |

14:20-14:40 |

Massively Parallel Processor

Architectures: A Co-design Approach

Hritam Dutta, Frank Hannig, Alexey

Kupriyanov, Dmitrij Kissler, Jürgen Teich,

Rainer Schaffer, Sebastian Siegel, Renate Merker,

Bernard Pottier

Department of Computer Science, University of Erlangen-Nuremberg, Germany

Institute of Circuits and Systems, Dresden University of Technology, Germany

Architectures et Systèmes, Université de Bretagne Occidentale, France

|

|

14:40-15:00 |

Stack processor architecture and development

methods suitable for dependable applications

Mehdi Jallouli, Camille Diou, Fabrice Monteiro

Laboratoire Interfaces, Capteurs et Microélectronique,

Université Paul Verlaine, France |

| 15:00-16:00 |

Session 4: Mapping and Programming

Models

Session Chair: Heiko Hinkelmann |

|

15:00-15:20 |

Coordinated concurrent memory

accesses on a reconfigurable multimedia processor

Samar Yazdani, Joel Cambonie,

Bernard Pottier

STMicroelectronics, Université de Bretagne

Occidentale, France

|

| |

15:20-15:40 |

Experiments of Using Object

Oriented Programming Methods in High Level

Sanna Määttä and Jari Nurmi

Tampere University of Technology, Finland |

|

15:40-16:00 |

Multiple Abstraction Views of FPGA to Map Parallel

Application

Sébastien Le Beux,

Philippe Marquet, Jean-Luc Dekeyser

LIFL and INRIA-Futurs University of Lille, France |

| 16:00-16:30 |

Coffee Break |

16:30-18:00  |

Panel Session

Programmability and debug issues on reconfigurable and

communication-centric SoCs

|

| 19:30 |

Dining Cocktail |

|

| |

| Tuesday June

19th |

| |

9:00-9:45

|

Keynote

2

Networks-on-chips: The communication challenge for future

SoC platforms

Fernando Gehm Moraes

Chair : Manfred Glesner

|

| 9:45-10:45 |

Session 5: NOC Architectures

Session Chair: Ian O'Connor |

|

9:45-10:05 |

A Dynamic Communication Structure

for Dynamically Reconfigurable FPGAs

S. Jovanovic, C. Tanougast, C. Bobda

and S. Weber

Université Henri Poincaré - Nancy

1 - LIEN, France

Department of Computer Science University

of Kaiserslautern, Germany

|

|

10:05-10:25 |

Adaptive Network for Multiprocessing

in Programmable Logic Devices

Thomas Haller, Christophe Bobda

Department of Computer Science University of Kaiserslautern, Germany

|

Due

to technical problem this video is not available |

10:25-10:45 |

Long-Range Dependence and On-chip

Processor Traffic

Antoine Scherrer, Antoine Fraboulet,

Tanguy Risset

COMPSYS - CITI - INSA Lyon, France |

| 10:45-11:15 |

Coffee Break |

| 11:15-11:55 |

Session 6: Test and verification

in ReCoSoC Platforms

Session Chair: Bruno Rouzeyre |

|

11:15-11:35 |

FPGA Prototyping of a Scan

Based System-On-Chip Design

Brendan Mullane, Chen-Huan Chiang,

Michael Higgins, Ciaran MacNamee, Tapan J Chakraborty,

Thomas B Cook

Industrial Engineering Test Development,

Alcatel-Lucent

Dept. of Electronic and Computer Engineering,

Circuits and Systems Research Center (CSRC),

University of Limerick, Ireland

|

|

11:35-11:55 |

Latch Inference for Equivalence

Checking

Anatol Ursu

Synplicity, France

|

| 12:00-13:30 |

Lunch |

| 13:30-14:50 |

Session 7: Security Issues

in ReCoSoC Platforms

Session Chair: Kris Gaj |

|

13:30-13:50 |

A Dependable Parallel Architecture

for SBoxes

G. Di Natale, M. L. Flottes, B. Rouzeyre

LIRMM, University of Montpellier 2 / CNRS, France

|

|

13:50-14:10 |

IBC-EI: An Instruction Based

Compression method with Encryption and Integrity Checking

Eduardo Wanderley, Reouven Elbaz,

Lionel Torres, Gilles Sassatelli, Romain Vaslin,

Guy Gogniat, Jean-Philippe Diguet

Dept. Informatics, CEFET-RN, Brazil

LIRMM Laboratory, CNRS,

Université de Montpellier 2, France

LESTER Laboratory

University of South Britany, France

Dept of Electrical Engineering,

Princeton University, USA

|

|

14:10-14:30 |

Low latency solution for confidentiality and

integrity checking in embedded systems with off-chip memory

Romain Vaslin, Guy Gogniat, Eduardo Wanderley,

Russell Tessier, Wayne Burleson

University of Massachusetts, USA

University of Bretagne

Sud LESTER, France |

|

14:30-14:50 |

Self-adaptive Security at Application Level:

a Proposal

Alberto Ferrante, Antonio

Vincenzo Taddeo, Mariagiovanna Sami, Fabrizio Mantovani,

Jurijs Fridkins

ALaRI, Faculty of Informatics, University of Lugano, Switzerland |

14:50-16:30

|

Panel Session

Security/Cryptography |

| 18:00 |

Beach Departure |

|

| Wednesday June

20th |

| |

| 9:30-10:30 |

Session

8: Applications of ReCoSoC systems

Session Chair: Tanguy Risset |

|

9:30-9:50 |

FPGA Implemenatation of an

Adaptive Filtering: Application on ECG Signal Artefact

Suppression in MRI Environment

Hervé Berviller, Vincent Frick, Philippe

Bougeot, Jean-Philippe Blonde, Julien Oster,

Jacques Felblinger

Institut d’Électronique du Solide

et des Systèmes ULP/CNRS, France

Imagerie Adaptative

Diagnostique et Interventionnelle UHP/INSERM, France |

|

9:50-10:10 |

Implementation of a 2D low-pass image filtering

algorithm on a reconfigurable device

Fabio

Garzia, Claudio Brunelli, Andrea Ferro, Jari

Nurmi

Tampere University of Technology, Finland

Universita a

degli Studi di Bologna, Italy |

|

10:10-10:30 |

Special Purpose Multi-processor for On-line

Fault Detection on Induction Motors during Steady State

Jose A. Vite-Frias, Rene de J. Romero-Troncoso, Alejandro

Ordaz-Moreno, Jesus R. Rivera-Guillen, Arturo Garcia-Perez

HSPdigital FIMEE - University of Guanajuato, Mexico |

| 10:30-11:00 |

Coffee Break |

| 11:00-11:40 |

Session 9: Design of Reconfigurable

Architectures

Session Chair: Fernando Moraes |

|

11:00-11:20 |

A Family of Ultra-Fine Grain

CNTFET-based Reconfigurable Logic Gates

J. Liu, I. O’Connor, D. Navarro, F. Gaffiot

University of Lyon – Lyon Institute of Nanotechnology

(INL), France

|

|

11:20-11:40 |

On the Design of a Reconfigurable Multiplier

for Integer and Galois Field Multiplication

H. Hinkelmann, T. Murgan, G. Liu, P. Zipf, and M.

Glesner

Institute of Microelectronic Systems Darmstadt University

of Technology, Germany |

11:40-12:00

|

Closing session

|

|

| |

| |

| Posters and Interactive presentation |

| |

Automatic Generation of Adaptive Multiprocessor Systems

Thomas Haller, José Rodrigo Azambuja, Christophe

Bobda

Department of Computer Science, University of Kaiserslautern, Germany |

| |

Dedicated Multiprocessing Unit for Polynomial Evaluation

on FPGA in CNC Profile Generation

Jesus Rooney

Rivera-Guillen, Rene de J. Romero-Troncoso, Alejandro Ordaz-Moreno,

Jose Alberto Vite-Frias

HSPdigital FIMEE - University of Guanajuato, Mexico |

| |

Dedicated Special Purpose Multiprocessor System for

the Diagnostic of Rotor Bar Breakage on Inductio

Alejandro Ordaz-Moreno, Rene de J. Romero-Troncoso, J. Alberto

Vite-Frias, J. Rooney Rivera-Guillen, Arturo Garcia-Perez

HSPdigital FIMEE - University of Guanajuato, Mexico |

| |

Selecting the Optimal Number of Functional Units of

Digital Real Time Systems

Wladyslaw Szczesniak

Gdansk University of Technology, Poland |

| |

| |

|

|

|