AWARDS

|

NXP was awarded "Best Paper at the VLSI Test Symposium 2007" which was handed out last week at this year's VTS in San Diego California. The joint paper "Diagnosis of Full Open Defects in Interconnecting Lines" between Universitat Politècnica de Catalunya, Barcelona, Spain, and NXP develops a method to determine the exact location of the interruption with micrometer accuracy from electrical measures only.

Understanding how devices fail is one of the most powerful methods to increase yield (avoid defects) and - increasingly important - to improve test methods (and hence outgoing quality). Many of our customers insist that we diagnose fully the root cause of field returns, because they realize that this is our only chance to learn from mistakes. Electrical diagnosis - that is, without physical deconstruction of the device - is the cheapest way and hence can be performed on volume, to gain statistical significance. It is very often also the first step before any detailed physical examination and essential to increase the success rate. Therefore, the Sematech ITRS roadmap indicate that electrical methods need be developed, which can localize the defect to not more than 10mm wire length.

The paper "Diagnosis of Full Open Defects in Interconnecting Lines", presented at VLSI Test Symposium (April 27-May 1, 2008) accomplishes just that: With our current diagnosis tools (FALOC), it is already possible to locate the defect typically within several hundred micrometers. The proposed method then determines a precise location for a line break as follows: The voltage on the floating part of the net is calculated based on the capacitive coupling to neighboring nets. This voltage in turn is used to predict a leakage current. The process is repeated for hundreds of circuit states (test patterns) and potential defect locations. The resulting pattern of passing and failing tests and defect currents can be compared with measurements to determine the true defect location.

The paper was a joint paper between Universitat Politècnica de Catalunya, Barcelona, Spain, and NXP. NXP colleagues that received the award: Stefan Eichenberger, Camelia Hora, Bram Kruseman, Maurice Lousberg, Ananta Majhi. |

2008

PUBLICATIONS

LIRMM

E. Cota, J. Dalmasso, M.-L. Flottes, B. Rouzeyre, “Improving the Test of NoC-Based SoCs with Help of Compression Schemes”, proceedings of ISVLSI'08: IEEE Computer Society Annual Symposium on VLSI, Montpellier, France, 2008

J. Dalmasso, M.-L. Flottes, B. Rouzeyre, “Compression-based SoC Test Infrastructures”, to appear in "VLSI-SoC Book", Springer, 2008

E. Simeu, H.N. Nguyen, P. Cauvet, S. Mir, L. Rufer and R. Khereddine. Using signal envelope detection for online and offline RF MEMS switch testing. Journal of VLSI Design, Ed. Hindawi (to appear).

L. Dilillo, P. Girard, C. Landrault, S. Pravossoudovitch, A. Virazel, M. Bastian and V. Gouin, “Impact of Technology Scaling on Defects and Parameter Deviations in Embedded SRAMs”, IEEE VLSI Test Symposium, Innovative Practice Session on “Testing Embedded Memories”, Santa Clara, USA, 2008.

A. Ney, P. Girard, S. Pravossoudovitch, A. Virazel, M. Bastian et V. Gouin, “A Design-for-Diagnosis Technique for SRAM Write Drivers”, proceedings of ACM/IEEE Design, Automation and Test in Europe, Munich, Germany, 2008.

A. Ney, A. Bosio, L. Dilillo, P. Girard, S. Pravossoudovitch et A. Virazel, “A Signature-based Approach for Diagnosis of Dynamic Faults in SRAMs”, proceedings of IEEE International Conference on Design & Test of Integrated Systems, Touzeur, Tunisia, 2008.

A. Ney, A. Bosio, L. Dilillo, P. Girard, S. Pravossoudovitch, A. Virazel et M. Bastian, “A History-Based Diagnosis Technique for Static and Dynamic Faults in SRAMs”, to appear in IEEE International Test Conference, Santa Clara, USA, 2008.

A. Ney, P. Girard, S. Pravossoudovitch, A. Virazel, M. Bastian et V. Gouin, “An SRAM Design-for-Diagnosis Solution based on Write Driver Voltage Sensing”, proceedings of IEEE VLSI Test Symposium, pp. 89-94, San Diego, USA, 2008.

A. Rousset, A. Bosio, P. Girard, C. Landrault, S. Pravossoudovitch et A. Virazel, “Improving Diagnosis Resolution Without Physical Information”, proceedings of IEEE International Symposium on Electronic Design, Test & Applications, Hong Kong, China, 2008

A. Ney, P. Girard, S. Pravossoudovitch, A. Virazel et M. Bastian, “Analysis of Resistive-Open Defects in SRAM Sense Amplifiers”, to appear in IEEE Transactions on VLSI, 2009.

A. Ney, L. Dilillo, P. Girard, S. Pravossoudovitch, A. Virazel, M. Bastian et V. Gouin, “A New Design-for-Test Technique for SRAM Core-Cell Stability Faults”, to be presented at ACM/IEEE Design, Automation and Test in Europe, Nice, France, 20-24 April 2009.

L. Dilillo, P. Girard, C. Landrault, S. Pravossoudovitch, A. Virazel, M. Bastian and V. Gouin, “Impact of Technology Scaling on Defects and Parameter Deviations in Embedded SRAMs”, IEEE VLSI Test Symposium, Innovative Practice Session on “Testing Embedded Memories”, Santa Clara, USA, 2008.

A. Ney, P. Girard, S. Pravossoudovitch, A. Virazel, M. Bastian et V. Gouin, “A Design-for-Diagnosis Technique for SRAM Write Drivers”, proceedings of ACM/IEEE Design, Automation and Test in Europe, Munich, Germany, 2008.

A. Ney, A. Bosio, L. Dilillo, P. Girard, S. Pravossoudovitch et A. Virazel, “A Signature-based Approach for Diagnosis of Dynamic Faults in SRAMs”, proceedings of IEEE International Conference on Design & Test of Integrated Systems, Touzeur, Tunisia, 2008.

A. Ney, A. Bosio, L. Dilillo, P. Girard, S. Pravossoudovitch, A. Virazel et M. Bastian, “A History-Based Diagnosis Technique for Static and Dynamic Faults in SRAMs”, IEEE International Test Conference, paper 3.2, CDRom Proceedings, Santa Clara, USA, 2008.

A. Ney, P. Girard, S. Pravossoudovitch, A. Virazel, M. Bastian et V. Gouin, “An SRAM Design-for-Diagnosis Solution based on Write Driver Voltage Sensing”, proceedings of IEEE VLSI Test Symposium, pp. 89-94, San Diego, USA, 2008.

A. Rousset, A. Bosio, P. Girard, C. Landrault, S. Pravossoudovitch et A. Virazel, “Improving Diagnosis Resolution Without Physical Information”, proceedings of IEEE International Symposium on Electronic Design, Test & Applications, Hong Kong, China, 2008.

E. Cota, J. Dalmasso, M.-L. Flottes, B. Rouzeyre, “Improving the Test of NoC-Based SoCs with Help of Compression Schemes”, proceedings of ISVLSI'08: IEEE Computer Society Annual Symposium on VLSI, Montpellier, France, 2008

J. Dalmasso, M.-L. Flottes, B. Rouzeyre, “Compression-based SoC Test Infrastructures”, in "VLSI-SoC Book", Springer, 2008

NXP NL

A. Zjajo, J. Pineda de Gyvez, “Analog Automatic Test Pattern Generation for Quasi-Static Structural Test”, IEEE Transactions on VLSI Systems, accepted for publication.

F. de Jong, A. Biewenga, “The PinCap sensor”, accepted for publication at ITC2008.

Vladimir Zivkovic, Jan Schat, Geert Seuren, Frank van der Heyden, “A Generic Infrastructure for Testing SoC’s with Mixed-Signal/RF Modules,” Proc. of the IEEE International Mixed-Signal Test Workshop (IMSTW), Edinburg, June 2006, pp. 90-95.

Vladimir Zivkovic, Frank van der Heyden, Frans de Jong, Guido Gronthoud, “Analog Test Bus Infrastructure for RF/AMS Modules in Core-based Design,” Proc. of the 13-th IEEE European Test Symposium (ETS), Verbania, Italy, May 2008.

Vladimir Zivkovic, Rene Jonker, “Test Verification and Program Generation for Modular System-on_chips with Mixed-Signal Cores,” Proc. of the 26-th IEEE VLSI Test Symposium (VTS), San Diego, USA, April 2008.

Vladimir Zivkovic, Jan Schat, Frank van der Heyden, Geert Seuren, “Core-Based Testing of Embedded Mixed-Signal Modules in a SoC,” accepted as a publication in a regular issue of IEEE Design & Test of Computers.

“Fast Fault Diagnosis for Analog ICs” presented at the AEC Reliability Workshop, May 6-8, Novi, Michigan, USA

A. Zjajo, J. Pineda de Gyvez, “Diagnostic Analysis of Static Errors in Multi-Step Analog to Digital Converters”, Proceedings of IEEE Design, Automation and Test in Europe Conference, pp.74-79, 2008

X. Sheng, H. Kerkoff, A. Zjajo, G. Gronthoud, “Exploring Dynamics of Embedded ADC through Adapted Digital Input Stimuli”, IEEE International Mixed-Signals, Sensors and Systems Test Workshop, to be presented

NXP FR & LIRMM

Journals:

V. Kerzérho, P. Cauvet, S. Bernard, F. Azaïs, M. Renovell, M. Comte and O.Chakib, ”ADC Production Test Technique Using Low Resolution Arbitrary Waveform Generator”, Journal of VLSI Design, vol. 2008, Article ID 482159, 8 pages, 2008. doi:10.1155/2008/482159

Book:

S. Bernard, P. Cauvet, M. Renovell, “System On Chip Test Architectures”, Chapter 5, pp225-261, ISBN 978-0-12-373973-5 Morgan-Kaufmann Publishers.

Thesis Reports:

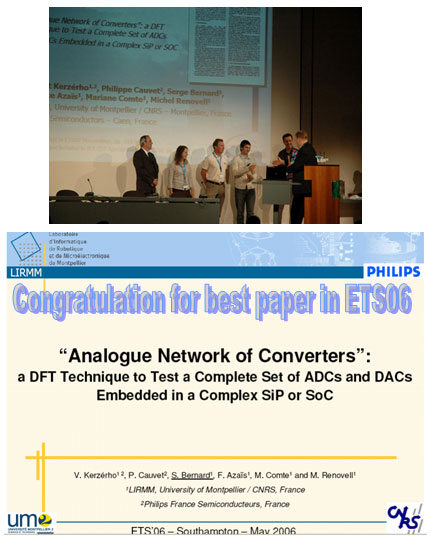

Vincent Kerzérho, "“Analogue Network of Converters”: a DfT Technique to Test a Complete Set of ADCs and DACs Embedded in a Complex SiP or SoC" PhD, University of Montpellier II. Thesis defense date: April 22 2008

Vincent Fresnaud, "Etude et compensation des non-linéarités de Convertisseur Analogique/ Numérique utilisant une architecture à repliement et interpolation" PhD University of Bordeaux I. Thesis defense date: April 7 2008.

Q-Star Test

In cooperation with LSI:

Richard Durant, LSI * Daniel Ahrens, LSI * Ariadne Salagianis, Verigy, Dynamic Supply Current Signature (Iddcs) Analysis Using the Qstar Module on V93000, Verigy VOICE08 conference, San Jose, Ca, USA, September 2008.

In cooperation with Avago:

P. O'Neill, Avago Technologies, Production Multivariate Outlier Detection Using Principal Components, Proceedings of the International Test Conference (ITC) 2008, paper 1.2, Santa Clara, Ca, USA, October 2008.

STMicroelectronics + TIMA

H. Stratigopoulos, J. Tongbong and S. Mir. A general method to evaluate RF BIST techniques based on non-parametric density estimation. Design and Test in Europe Conference, Munich, Germany, March 2008, pp. 68-73.

S. Mir. Evaluation of mixed-signal/RF DFT solutions for SiP devices using statistical techniques. Workshop on Reliability & DfX engineering for System-in-Package Technologies, Invited Talk, Pallanza, Italy, May 2008.

M. Dubois, N. Chouba and S. Mir. Calibrage automatique d’un convertisseur Sigma-Delta utilisant un BIST. 11th Journées Nationales du Réseau Doctoral en Microélectronique, Bordeaux, France, May, 2008.

Asquini, F. Badets, S. Mir, J.L. Carbonero and L. Bouzaida. PFD output monitoring for RF PLL BIST. 14th IEEE International Mixed-Signals Testing Workhop, Vancouver, Canada, June 2008.

Bounceur and S. Mir. Estimation of test metrics for AMS/RF BIST using Copulas. 14th IEEE International Mixed-Signals Testing Workhop, Vancouver, Canada, June 2008.

N. Akkouche, S. Mir, E. Simeu and H. Stratigopoulos. Réduction de tests fonctionnels en utilisant des techniques d’estimation non paramétrique. 11th Journées Nationales du Réseau Doctoral en Microélectronique, Bordeaux, France, May, 2008.

NXP FR +TIMA

E. Simeu, H.N. Nguyen, P. Cauvet, S. Mir, L. Rufer and R. Khereddine. Using signal envelope detection for online and offline RF MEMS switch testing. Journal of VLSI Design, Ed. Hindawi, Vol. 2008, Article ID 294014, 10 pages, doi:10.1155/2008/294014

Infineon [AT]

R.Arnold, C.Kupnick. Automatic Functional JTAG Test Pattern Generation for Embedded Analog Power Modules with Standardized Test Access. ITG Testmethoden und Zuverlässigkeit, Vienna, February 2008

Q-Star Test

B. Straka, H. Manhaeve, J. Brenkus and S. Kerckenaere, Theoretical and Practical Aspects of IDDQ Settling - Impact on Measurement Timing and Quality, Proceedings of the 2008 Design, Automation and Test In Europe Conference, pp. 1310-1315

H. Manhaeve, The Quest for Test: Will Redundancy Cover All?, Keynote presentation, Proceedings of the 2008 IEEE Design and Diagnostics of Electronic Circuits and systems Workshop (DDECS2008), p. 3

H.Manhaeve, Automating Test Development for Mixed-Signal and RF circuits – Can Current Test Help?, Contribution to the IP Session 3C: Automatic Test Development for Mixed-Signal/RF Circuits of the 26th IEEE VLSI Test Symposium (VTS08) – On CDROM

H. Manhaeve, S. Kerckenaere, G. Eide, J. Brenkus, The (Black) Art of Optimizing Test Vector Generation, Poster presentation at the 13th IEEE European Test Symposium (ETS08) – On CDROM

H. Manhaeve, Current Test – An Application Perspective, Presentation at the 13th IEEE European Test Symposium (ETS08) – On CDROM

Contributions to workshops, exhibitions, conferences, journals

LIRMM

Conference Committees: ITC’08 (Program Committee), VTS’08 (Program Committee), ETS’08 (Steering Committee, Program Chair, Topic Chair, Publication Chair), ATS’08 (Program Committee), DATE’08 (Test Track Chair, Program Committee), DDECS’08 (Steering Committee, Program Committee), IOLTS’08 (Program Committee), LATW’08 (Program Committee).

Patrick Girard, Vice-Chair of the European Test Technology Technical Council (ETTTC), Program Chair of ETS’08 in Italy.

Patrick Girard and Michel Renovell, Members of the Editorial Board of ‘Journal of Electronic Testing: Theory and Applications (JETTA), published by Springer Science.

Q-Star Test

Exhibition of Products and Services at the Design, Automation & Test In Europe conference (DATE08) exhibition floor

Program Committee member of and reviewer for various international events (DATE, ITC, ETS, DDECS, …)

H. Manhaeve:

moderator of session 5.5 “Statistical, Physical Defect Based Testing” of the Design, Automation & Test In Europe conference (DATE08)

Keynote presentation at the 2008 IEEE Design and Diagnostics of Electronic Circuits and systems Workshop (DDECS2008)

Presentation at the 26th IEEE VLSI Test Symposium (VTS08)

Paper and poster presentation at the 13th IEEE European Test Symposium (ETS08)

Moderator of session 2C “ ATE Architectures” of the 13th IEEE European Test Symposium (ETS08)

NXP NL

NXP NL has contributed to the following activities:

VTS-08: Industrial Practice Session organization and memory test contribution

ETS-08: Paper accepted for publication

A World without Test Escapes: The Use of Volume Diagnosis to Improve Test Quality, accepted for publication at ITC 2008.

Full Open Defects in Nanometric CMOS, accepted and presented in VTS 2008

Time-dependent Behavior of Full Open Defects in Interconnecting Lines accepted for publication at ITC 2008.

Demo on “Automatic Test Development for System-on-Chips with Analog and Mixed-Signal Cores” at the Nanoelectronics Forum 2008 in Paris

K. Veelenturf represented the NanoTEST team at a panel session on “Collaborative Test Research in Europe” at ETS2008 in Verbania, Italy, May 2008.

Infineon-F & LIRMM

“An SRAM Design-for-Diagnosis Solution based on Write Driver Voltage Sensing”, Alexandre NEY, Patrick GIRARD, Serge PRAVOSSOUDOVITCH, Arnaud VIRAZEL, Magali BASTIAN , Vincent GOUIN, VTS08, 28-30 April 2008.

“A Design-for-Diagnosis Technique for SRAM Write Drivers”, Alexandre NEY, Patrick GIRARD, Serge PRAVOSSOUDOVITCH, Arnaud VIRAZEL, Magali BASTIAN , Vincent GOUIN, DATE08, 10-14 March 2008.

Infineon AT

R.Arnold, C.Kupnick: “Automatic Functional JTAG Test Pattern Generation for Embedded Analog Power Modules with Standardized Test Access”, submitted to: ITG Zuverläßigkeit von Schaltungen und Systemen, Vienna, April 2008

2007

PUBLICATIONS

INESC-ID

· José A. Soares Augusto and Carlos Beltrán Almeida, "A Tool for Single Fault Diagnosis in Linear Analog Circuits with Tolerance Using the T-vector Approach", accepted for presentation at the International Mixed Signals Testing Workshop, Póvoa de Varzim, June 2007.

· J. Semião, J. Freijedo, J. Rodríguez-Andina, F. Vargas, M. B. Santos, I. C. Teixeira, J. P. Teixeira, “Mixed-signal Design of Dynamic Delay Buffers to Improve Tolerance to Power Supply and Temperature Variations”, Proc. of the 13th. International Mixed Signals Testing Workshop (IMSTW’07), pp 130-135, ISBN 978-972-99181-2-4, Póvoa de Varzim, Portugal, June 18-20, 2007.

· J. Semião, J. Freijedo, J. Rodriguez-Andina, F. Vargas, M. Santos, I. Teixeira, J. Teixeira, “Enhancing the Tolerance to Power-Supply Instability in Digital Circuits”, Proc. of the IEEE Computer Society Annual Symposium on VLSI 2007 (ISVLSI’07), Porto Alegre, Brazil, May, 2007.

· J. Semião, J. Freijedo, J. Rodríguez−Andina, F. Vargas, M. Santos, I. Teixeira, J. Teixeira, “Improving Tolerance to Power-Supply and Temperature Variations in Synchronous Circuits”, Proceedings of the 10th. IEEE Workshop on Design and Diagnostics of Electronic Circuits and Systems (DDECS), pp. 295-300, Krakow, Poland, April 11-13, 2007.

· M. Rodriguez-Irago, J. Rodriguez-Andina, J. Semiao, F. Vargas, I. Teixeira, J. Teixeira, “A Model for the Analytical Definition of Multi-VDD, Multi-T Dynamic Tests in Nanometer Digital Circuits”, Proceedings of the 8th. IEEE Latin-American Test Workshop (LATW’07), Cuzco, Peru, March 11 - 14, 2007.

· J. Semião, M. Rodriguez-Irago, M. Santos, J. Teixeira, I. Teixeira, L. Piccoli, F. Vargas, J. Rodriguez-Andina, “Digital Circuit Signal Integrity Enhancement by Monitoring Power Grid Activity”, Proceedings of the 8th. IEEE Latin-American Test Workshop (LATW’07), Cuzco, Peru, March 11 - 14, 2007.

· José Fernandes, Marcelino Santos, Arlindo Oliveira, Joao Paulo Teixeira, Raoul Velazco, “Sensitivity to SEUs Evaluation using Probabilistic Testability Analysis at RTL”, IEEE Latin America Test Workshop (LATW), March 2007.

INESC Porto

· Hélio S. Mendonça, José Machado da Silva, José S. Matos, “Estimation of ADC’s SINAD after the Code Histogram Method”, accepted for publication in the IET Journal on Science, Measurement & Technology.

· José Machado da Silva, Pedro Mota, John Long, “On-chip Estimation of RF Power Amplifier’s Non-Linearity”, Workshop on On-Chip/Off-Chip DC, RF and Microwave Measurement Modules for RFIC, SoC and SiP Self-Characterization, Self-Test, Self Debug and Diagnosis, (International Microwave Symposium), Honolulu, 4 June 2007.

· Pedro Mota, José Machado da Silva, John Long, “Estimation and adaptive correction of PA’s nonlinearities” 13th IEEE International Mixed Signals Testing Workshop, Póvoa de Varzim,Portugal, 18-20 June, 2007

· Manuel Cândido Santos, Vítor Grade Tavares, José Machado da Silva, Sebastian Tabarce, “A built-in methodology for resemblance gathering in RKII networks” 13th IEEE International Mixed Signals Testing Workshop, Póvoa de Varzim,Portugal, 18-20 June, 2007.

· Luís Rocha, Lukas Mol, Edmond Cretu, Reinoud Wolffenbuttel, José Machado da Silva, “Capacitive MEMS accelerometers testing mechanism for auto-calibration and long-term diagnostics”, 13th IEEE International Mixed Signals Testing Workshop, Póvoa de Varzim,Portugal, 18-20 June, 2007

Infineon FR & LIRMM

· L. Dilillo, P. Girard, S. Pravossoudovitch, A. Virazel et M. Bastian, “Analysis and Test of Resistive-Open Defects in SRAM Pre-Charge Circuits”, to appear in JETTA Journal of Electronic Testing - Theory and Applications, Springer, 2007.

· A. Ney, P. Girard, C. Landrault, S. Pravossoudovitch, A. Virazel et M. Bastian, “Slow Write Driver Faults in 65nm SRAM Technology: Analysis and March Test Solution”, ACM/IEEE Design, Automation and Test in Europe, , pp. 528-533, Nice, France, 16-20 April 2007.

· A. Ney, P. Girard, C. Landrault, S. Pravossoudovitch, A. Virazel et M. Bastian, “Un-Restored Destructive Write Faults due to Resistive-Open Defects in the Write Driver of SRAMs”, IEEE VLSI Test Symposium, pp. 361-366, Berkeley, USA, 6-10 May 2007.

· A. Ney, P. Girard, C. Landrault, S. Pravossoudovitch, A. Virazel et M. Bastian, “Dynamic Two-Cell Incorrect Read Fault due to Resistive-Open Defects in the Sense Amplifiers of SRAMs”, IEEE European Test Symposium, pp. 97-102, Freiburg, Germany, 20-24 May 2007.

· M. Bastian, V. Gouin, P. Girard, C. Landrault, A. Ney, S. Pravossoudovitch et A. Virazel, “Influence of Threshold Voltage Deviations on 90nm SRAM Core-Cell Behavior”, to appear in IEEE Asian Test Symposium, Beijing, China, 9-11 October 2007.

LIRMM

· A. Bosio, P. Girard, C. Landrault, S. Pravossoudovitch, A. Virazel et A. Rousset, “A Mixed Approach for Unified Logic Diagnosis”, IEEE Workshop on Design and Diagnostics of Electronic Circuits and Systems, pp. 239-242, Cracow, Poland, April 2007.

· A. Rousset, A. Bosio, P. Girard, C. Landrault, S. Pravossoudovitch et A. Virazel, “DERRIC: a Tool for Unified Logic Diagnosis”, IEEE European Test Symposium, pp. 13-18, Germany, Allemagne, 20-24 May 2007.

· A. Rousset, A. Bosio, P. Girard, C. Landrault, S. Pravossoudovitch et A. Virazel, “Fast Bridging Fault Diagnosis Using Logic Information”, to appear in IEEE Asian Test Symposium, Beijing, China, 9-11 October 2007.

· J. Dalmasso, M.L. Flottes, B. Rouzeyre "TAM Design and test data compression for SOC test cost reduction" inofrmal proceedings of the "European Test Symposium 2007" ETS'07, pp: 241-246

· E. Cota , J Dalmasso, M-L Flottes, B Rouzeyre "Improving NoC-Based Testing Through Compression Schemes" IEEE Workshop on Diagnostic Services in Networks-on-Chips – Test, Debug and On-Line Monitoring, Nice, 20 Avril 2007, pp:20-21

· Publications LIRMM/Philips -> See Report sent by Philippe Cauvet

NXP NL

· A. Zjajo, J. Barragan Asian, J. Pineda de Gyvez, “BIST Method for Die-Level Process Parameter Variation Monitoring in Analog/Mixed-Signal Integrated Circuits”, IEEE Proceedings of Design, Automation and Test Europe, pp. 1301-1306, 2007

· Xinyue Fan, Will R Moore, (Univ Oxford-UK), Camelia Hora, Guido Gronthoud (NXP), “'Extending Gate Level Diagnosis Tools to CMOS Intra-gate Faults”, IET Computers & Digital Techniques,

· R. Rodríguez-Montañés, D. Arumí, J. Figueras (UPC-Barcelona), S. Eichenberger, C. Hora, B. Kruseman, M. Lousberg, A.K. Majhi (NXP), “Diagnosis of Full Open Defects in Interconnecting Lines” accepted in VTS07, 6-10 May, CA, USA

· R. Rodríguez-Montañés, D. Arumí, J. Figueras (UPC-Barcelona), S. Eichenberger, C. Hora, B. Kruseman, M. Lousberg, A.K. Majhi (NXP), “Diagnosis of Bridging Defects Based on Current Signatures at Low Power Supply Voltages”, accepted in VTS07, 6-10 May, CA, USA

· A. Biewenga, F. De Jong, NXP Semiconductors “SiP-Test: Predicting Delivery Quality”, IEEE International Test Conference, Submission accepted to be published Q4

· Paul Wielage, Erik Jan Marinissen, Michel Altheimer, and Clemens Wouters, “Design and DfT of a High-Speed Area-Efficient Embedded Asynchronous FIFO”, Design, Automation, and Test in Europe (DATE'07), Nice, France, April 2007, pp. 853-858

· Tobias Dubois, Mohamed Azimane, Erik Larsson, Erik Jan Marinissen, Paul Wielage, and Clemens Wouters, “Test Quality Analysis and Improvement for an Embedded Asynchronous FIFO”, Design, Automation, and Test in Europe (DATE'07), Nice, France, April 2007, pp. 859-864

· Erik Jan Marinissen, Kees Goossens, Alexandre M. Amory, Marcelo Lubaszewski, Fernando Moraes, Pengwei Ren, Ardy van den Berg, Georgi Gaydadjiev, ”Test Wrapper Design for the Reuse of a Bus, NOC, or Other Functional Interconnect as Test Access Mechanism”, IEEE VLSI Test Symposium (VTS'07), Berkeley, CA, USA, May 2007

· Jeroen Geuzebroek, Erik Jan Marinissen, Ananta Majhi, Andreas Glowatz, and Friedrich Hapke, “Embedded Stuck-At-Fault Multi-Detect ATPG and Its Effect on the Detection of Unmodeled Defects”, Accepted at IEEE International Test Conference (ITC'07), Santa Clara, CA, USA, October 2007

STM

See TIMA publication list.

TIMA

· A. Bounceur, S. Mir, E. Simeu and L. Rolíndez. Estimation of test metrics for the optimisation of analogue circuit testing. Journal of Electronic Testing: Theory and Applications (to appear).

· N. Akkouche, A. Bounceur, S. Mir and E. Simeu. Functional test compaction by statistical modelling of analogue circuits. 13th IEEE International Mixed-Signals Testing Workhop, Porto, Portugal, June 2007, pp. 20-24.

· N. Akkouche, A. Bounceur and S. Mir. Réduction de tests fonctionnels par modélisation statistique des circuits analogiques. 10th Journées Nationales du Réseau Doctoral en Microélectronique, Lille, France, 14-16 May, 2007.

· A. Bounceur. Plateforme CAO pour le test des circuits mixtes. PhD Thesis. Institut National Polytechnique de Grenoble, France, April 2007.

· A. Bounceur, S. Mir, L. Rolíndez and E. Simeu. CAT platform for analogue and mixed-signal test evaluation and optimization. Chapter in Research trends in VLSI and Systems on Chip, G. De Micheli, S. Mir, R. Reis (Eds.), Springer Science+Business Media (to appear).

· L. Rolíndez, S. Mir, J.L. Carbonero, D. Goguet and N. Chouba. A stereo audio ADC architecture for embedded SNDR testing. IEEE International Test Conference, Santa Clara, USA, October 2007 (to appear).

· I. Mansouri. Réalisation d´un démonstrateur BIST pour un convertisseur analogique numérique Sigma-Delta. Final Year Project Report, Ecole Polytechnique de Tunisie, Juin 2007.

· A. Asquini, J.L. Carbonero and S. Mir. Test measurements evaluation for VCO and charge pump blocks in RF PLLs. SPIE International Symposium on Microtechnologies for the New Millenium, VLSI Circuits and Systems Conference, Gran Canaria, Spain, May 2007 (Proceedings to appear).

· J. Tongbong, S. Mir and J.L Carbonero. Evaluation of test measures for LNA production testing using a multinormal statistical model. Design and Test in Europe Conference, Nice, April 2007, pp. 731-736.

· S. Mir. Test intégré des circuits mixtes. Journées de la section électronique du Club EEA, SiP et SoC : nouvelles perspectives, nouveaux défis. Montpellier, France, March 2007.

· L. Rolíndez. Technique d´auto test pour des convertisseurs de signal Sigma-Delta. PhD Thesis. Institut National Polytechnique de Grenoble, France, February 2007.

· L. Rolíndez, S. Mir, A. Bounceur and J.L. Carbonero. A BIST Scheme for SNDR Testing of ADCs Using Sine-Wave Fitting. Journal of Electronic Testing: Theory and Applications, Springer Science+Business Media, 22(4-6), 2006, pp. 325-335.

· S. Mir. DFT for MEMS. RF-MEMS Workshop on Industry Applications: “RF power MEMS: reliability and applications”, Invited Talk, Barcelona, Spain, June 2007.

· Simeu, E., Cauvet, P., Nguyen, H. N., Mir, S., Rufer, L. Khereddine, R., Using signal envelope detection for RF MEMS switch testing, 13th IEEE International Mixed-Signals Testing Workshop 2007, Porto, Portugal, June 18-20 2007, pp. 68-73.

· H.N. Nguyen, L. Rufer, E. Simeu and S. Mir. RF MEMS series capacitive switch: test and diagnosis. Journées GDR SoC-SiP, Paris, France, Juin 2007.

· R. Khereddine, E. Simeu and S. Mir. Utilisation des techniques de regression pour le test et le diagnostic des composantes RF. Journées GDR SoC-SiP, Paris, France, Juin 2007.

Contributions to workshops, .....

INESC Porto

· The team was responsible for organizing and hosting the 13th edition of the IEEE International Mixed Signals Testing Workshop, held together with the 3rd GHz/Gbps Test Workshop, which took place in 18-20 June, at Póvoa de Varzim, Portugal.

· José Machado da Silva is program co-chair of the 2007 International Conference on Design & Technology of Integrated Systems in nanoscale era (DTIS’07), to be held in September 2-5, 2007, at Rabat, Morocco.

· Collaborated in the evaluation of papers submitted to the conferences IMSTW’07, DTIS’07, DCIS’07, ITC’07, and to the journals IET Science, Measurement & Technology, and IEEE Trans. on Instrumentation and Measurement, and IEEE Design and Test.

LIRMM

· Conference Committees: ITC’07 (Program Committee), VTS’07 (Program Committee), ETS’07 (Steering Committee, Topic Chair, Publication Chair, Embedded Tutorial Chair, Program Committee), ATS’07 (Program Committee), DAC’07 (Test Subcommittee Chair), DATE’07 (Test Track Chair, Program Committee), DDECS’07 (Program Chair, Steering Committee, Program Committee), IOLTS’07 (Program Committee), LATW’07 (Program Committee), DTIS’07 (Vice-General Chair, Program Committee).

· Christian Landrault and Michel Renovell, Members of Editorial Board of Journal of Electronic Testing: Theory and Applications (JETTA), published by Springer Science

· Patrick Girard, Vice-Chair of the European Test Technology Technical Council (ETTTC), Program Chair of ETS’08 in Italy.

NXP NL

· A fringe workshop to DATE’07 entitled ‘Diagnostic Services in Network-on-Chips: Test, Debug, and On-Line Monitoring’ has been set-up; NXP Research contributes as founder, General Chair, and contributor.

· Erik Jan Marinissen, 'Structural Test on Analog Design Is Not Feasible?', Organizer of Panel Session at NXP IC Test Symposium (NITS'07), Eindhoven, The Netherlands, June 2007

· Erik Jan Marinissen, 'Fostering Collaboration Between The Industry, Tool Vendors, and Academia', Moderator of Panel Session at IEEE Intnl. Workshop on Silicon Debug and Diagnosis (SDD'07), Freiburg, Germany, May 2007

· Erik Jan Marinissen, 'Test Access for Chips, Boards, and Multi-Board Systems: What Is Really Needed?', Moderator of Panel Session at IEEE European Test Symposium (ETS'07), Freiburg, Germany, May 2007

· Erik Jan Marinissen and Ben Bennetts, 'Logic BIST and Test Data Compression: Friends or Foes?', Organizers of Panel Session at IEEE European Test Symposium (ETS'07), Freiburg, Germany, May 2007

· Christian Landrault (LIRMM, France) and Erik Jan Marinissen (NXP Research, The Netherlands), Guest Editors of a Special Issue on ETS’06 of IET Computers and Digital Techniques, published May 2007.

· Erik Jan Marinissen (NXP Research, The Netherlands) and Nicola Nicolici (McMaster University, Hamilton, ON, Canada), Guest Editors of a Special Issue on Silicon Debug and Diagnosis of IET Computers and Digital Techniques (to be published in 2007).

· Rob Aitken (ARM, USA) and Erik Jan Marinissen (NXP Research), Guest Editors of a Special Issue on Silicon Debugging and Diagnosis of IEEE Design & Test of Computers (to be published in 2008).

· Erik Jan Marinissen, Member of Editorial Board of ‘Journal of Electronic Testing: Theory and Applications (JETTA), published by Springer Science + Business Media.

· Conference Committees: DATE’07 (Program Committee), DATE’07 Friday Workshop (General Chair), DDECS’07 (Steering Committee, Program Committee),DTIS’07 (Program Committee), ETS’07 (Topic Chair, Steering Committee), ETS’08 (Industrial-Relations Chair, Steering Committee), IOST3’07 (Program Committee), LATW’07 (Program Committee), SDD’07 (Steering Committee).

Temento

· Exhibition at Date 2007 in Nice: demonstration of

· AMBA bus analyzer prototype,

· TemStorage product,

· Last release of DiaLite product (version 4.7 pre-release)

2006

PUBLICATIONS

INESC-ID & INESC Porto

· A. Parreira, M.B. Santos, J.P. Teixeira, “BIST Architectures and Fault Emulation”, submited to the Proc. IEEE Latin America Test Workshop (LATW), 2006

INESC-Porto

Infineon AT

· H. Eichinger and G. Scheer, “SiP Testing An Industrial Case Study”, submitted to European Test Symposium, Southampton, May 2006

LIRMM

· Julien DALMASSO, Marie-Lise FLOTTES, Bruno ROUZEYRE, “Fitting ATE Channels with Scan Chains: a Comparison between a Test Data Compression Technique and Serial Loading of Scan Chains”, IEEE International Workshop on Electronic Design, Test & Applications, Kuala Lumpur, Malaysia, 17-19 January 2006.

LIRMM & Infineon FR

· P. Girard, S. Pravossoudovitch, A. Virazel, M. Bastian, “Failure Mechanisms due to Process Variations in Nanoscale SRAM Core-cells”, submitted to IEEE European Test Symposium 2006.

LIRMM & Philips FR

· V. Kerzérho, P. Cauvet, S. Bernard, F. Azais, M. Comte and M. Renovell, “A novel DFT technique to test a complete set of ADCs and DACs embedded in a complex SiP”, submitted to Design & Test Conference 2006.

· V. Kerzérho, P. Cauvet, S. Bernard, F. Azais, M. Comte and M. Renovell, “Analog Network of Converters: A DFT technique to test a complete set of ADCs and DACs embedded in a complex SiP or SOC, submitted to IEEE European Test Symposium 2006.

· V. Fresnaud, L. Bossuet, D. Dallet, S. Bernard, J.M. Janik, B. Agnus, Ph. Cauvet, Ph. Gandy “ A Low Cost Alternative Method for Harmonics Estimation in a BIST context”, submitted to IEEE European Test Symposium 2006

Philips NL

· S. Krishnan and A. Zjajo, "An Industrial Approach to Re-order Integrated Circuits Tests to Maximize Test Benefit," submitted to European Test Symposium 2006

· Lei Ma, G. Seuren, R. van. Rijsinge, C. Bastiaansen and L. van der Dussen, “Design-based Structural Test Method for Stereo DAC”, submitted to ETS 2006.

TIMA

· A. Dhayni, S. Mir, L. Rufer and A. Bounceur. Pseudorandom functional BIST for linear and non-linear MEMS. In Design and Test Conference in Europe, Munich, Germany, 2006 (to appear).

· L. Rolíndez, S. Mir, A. Bounceur and J.L. Carbonéro. “A Signal to Noise Ratio BIST for SD Analog-to-Digital Converters”. In 24th VLSI Test Symposium, Berkeley, California, USA, April-May 2006, (to appear).

2005

PUBLICATIONS

INESC-ID & INESC Porto & TECMIC

· J. Soares Augusto, Selection of Diagnosis Variables for Single Fault Diagnosis in Linear Circuits, IEEE European Test Symposium (ETS), Tallinn, Estonia, May 2005.

· Tiago Veiga, C.Beltrán Almeida, J. Soares Augusto, Efficient Analog Fault Simulation en AC Circuits, IEEE European Test Symposium (ETS), Tallinn, Estonia, May 2005.

· M. Rodriguez-Irago, J. Rodriguez Andina, D. Barros Júnior, F. Vargas, M.B. Santos, I.M. Teixeira, J. P. Teixeira, "Using Multi-Clock Schemes and Multi-VDD Test for Dynamic Fault Detection in Digital Systems", IEEE Latin American Test Workshop (LATW), Salvador, Bahia, Brazil, February 2005.

· D. Barros Júnior, M. Rodriguez-Irago, M.B. Santos, I.C. Teixeira, F. Vargas and J.P. Teixeira, Fault Modeling and Simulation of Power Supply Voltage Transients in Digital Systems on a Chip, Journal of Electronic Testing, Theory and Application (JETTA), vol.21, pp. 349-363, Kluwer Academic Publishers, August, 2005

· M. Rodriguez-Irago, J. J. Rodríguez Andina, F. Vargas, M. B. Santos, I. C. Teixeira and J. P. Teixeira, Multiple-Clock and Multi-VDD Schemes for Dynamic Fault Detection in Nanometer Digital Circuits, Proc. of the 20th. Conf. On Design of Circuits and Integrated Systems (DCIS), ISBN (full paper in CD-ROM format), November, 2005

· M. Rodriguez-Irago, J. Rodriguez Andina, F. Vargas, M.B. Santos, I.M. Teixeira and J. P. Teixeira, Dynamic Fault Test and Diagnosis in Digital Systems Using Multiple Clock Schemes and Multi-VDD Test, Proc. IEEE International On-Line Test Symposium (IOLTS), pp. 281-286, July, 2005.

INESC-ID & INESC Porto

· J. Machado da Silva, Low-Power In-Circuit Testing of a LNA, International Mixed-Signal Test Workshop (IMSTW), Cannes, France, June 2005.

· José Machado da Silva, Gabriel Pinho, and José S. Matos, "Design for Embedded Testing of an LNA", Abstract Book and CD-ROM of the XX Conference on Design of Circuits and Integrated Systems, Lisboa, November 2005.

· Francisco X. Duarte, José C. Alves, José Machado da Silva, Gabriel Pinho, and José S. Matos, "A High Level Test Processor and Test Program Generator", Abstract Book and CD-ROM of the XX Conference on Design of Circuits and Integrated Systems, Lisboa, November 2005.

· Francisco X. Duarte, José Machado da Silva, José C. Alves, Gabriel Pinho, and José S. Matos, "`A Processor for Testing Mixed-Signal Cores in System-on-Chip"', Proceedings of the 8th Digital System Design, pp. 184-191, Porto, September 2005.

Infineon AT

· Reithofer, Testing Integrated Pressure Sensors on Wafer Level, 12th Annual KGD Packaging & Test Workshop, Napa, September 2005.

LIRMM & Infineon FR

· S. Borri, M. Hage Hassan, L. Dilillo, P. Girard, S. Pravossoudovitch et A. Virazel, Analysis of Dynamic Defects in Embedded-SRAMs: Implications for Memory Test, JETTA Journal of Electronic Testing - Theory and Applications, Vol. 21, N° 2, pp. 169-179, Avril 2005.

· L. Dilillo, P. Girard, S. Pravossoudovitch, A. Virazel et M. Bastian Hage-Hassan, Test Solutions for Dynamic Faults in SRAM Memories, Medea+ Design Automation Conference, Paris, France, 22-25 May 2005.

· L. Dilillo, P. Girard, S. Pravossoudovitch, A. Virazel et M. Bastian Hage-Hassan, Resistive-Open Defect Injection in SRAM Core-cell: Analysis and Comparison between 0.13 ìm and 90 nm Technologies, ACM/IEEE Design Automation Conference, Anaheim, USA, 13-17 June 2005.

· L. Dilillo, P. Girard, S. Pravossoudovitch, A. Virazel et M. Bastian Hage-Hassan, Data Retention Fault in SRAM Memories: Analysis and Detection Procedures, IEEE VLSI Test Symposium, Palm Springs, USA, 1-5 May 2005.

· L. Dilillo, P. Girard, S. Pravossoudovitch, A. Virazel et M. Bastian Hage-Hassan, Resistive-Open Defect Influence in SRAM Pre-charge Circuits: Analysis and Characterization, IEEE European Test Symposium, Tallinn, Estonia, 22-25 May 2005.

· L. Dilillo, P. Girard, S. Pravossoudovitch, A. Virazel, M. Bastian Hage-Hassan, Efficient Test of Dynamic Read Destructive Faults in SRAM Memories, IEEE Latin American Test Workshop, pp. 40-45, Salvador Bahia, Brésil, 30 Mars 2 April 2005.

· L. Dilillo, P. Girard, S. Pravossoudovitch, A. Virazel, S. Borri, M. Hage-Hassan, Efficient March Test Procedure for Dynamic Read Destructive Fault Detection in SRAM Memories, JETTA Journal of Electronic Testing - Theory and Applications, Vol. 21, N° 5, pp. 551-561, October 2005.

LIRMM & Philips FR

· V.Kerzérho, S.Bernard, J.M.Janik, P.Cauvet, "Comparison between Spectral-based Methods for INL Estimation And Feasibility of Their Implantation, IEEE International Mixed-Signal Testing Workshop, June 2005.

Philips NL

· A. K. Majhi, G. Gronthoud, F. Bowen, S. Eichenberger, Testing for Small Delay Faults - Methods, Challenges, Test Cost and Quality, IEEE VLSI Test Symposium (VTS), May 200

· X. Fan, W. Moore, C. Hora, G. Gronthoud, Stuck-open Fault Diagnosis with Stuck-at Model, IEEE European Test Symposium (ETS), May 2005.

· X. Fan, W. Moore, C. Hora, G. Gronthoud, Stuck-Open Fault Diagnosis with Stuck-At Model, IEEE International Test Conference (ITC), November 2005.

· A. K. Majhi, M. Azimane, G. Gronthoud, M. Lousberg, F. Bowen, S. Eichenberger, Memory Testing Under Different Stress Conditions: An Industrial Evaluation, IEEE DATE-2005, Munich, Germany, March 2005.

· M. Azimane, A. K. Majhi, G. Gronthoud, M. Lousberg, S. Eichenberger and A. L. Ruiz, A New Algorithm for Dynamic Faults Detection in RAMs, IEEE VLSI Test Symposium (VTS), May 2005.

· T. Waayers, R. Morren and J. G. Grandi, Definition of a robust Modular SOC Test Architecture; Resurrection of the single TAM daisy-chain, ITC 2005; IEEE Int. Test Conf. (Austin, TX ).

· T. Waayers, E. J. Marinissen and G. E. A. Lousberg, IEEE Std 1500 Compliant Infrastructure for Modular SOC Testing, ATS 2005; 14th IEEE Asian Test Symp. (Kolkata, India).

· A. Sehgal, S. K. Goel, E. J. Marinissen and K. Chakrabarty, Hierarchy-Aware and Area-Efficient Test Infrastructure Design for Core-Based System-Chips, ITC 2005; IEEE Int. Test Conf. (Austin, TX ).

· S.K. Goel, E.J. Marinissen, On-Chip Test Infrastructure Design for Optimal Multi-Site Testing of System Chips, Design, Automation, and Test Europe (DATE), Mar 2005.

· A. Zjajo, Jose Pineda de Gyvez and G. Gronthoud, A Quasi-Static Approach for Detection and Simulation of Parametric Faults in Analog and Mixed-Signal Circuits, IMSTW 2005; 11th Int. Mixed-Signals Testing Workshop (Cannes Fr).

· E. Silva, Jose Pineda de Gyvez and G. Gronthoud, Functional vs. Multi-VDD Testing of RF Circuits, WTW 2005; 4th Workshop Test Wireless Circuits and Systems (Cannes Fr).

· E. Silva, E. Silva, Jose Pineda de Gyvez and G. Gronthoud, Functional vs. Multi-VDD Testing of RF Circuits, ITC 2005; IEEE Int. Test Conf. (Austin, TX ).

· G.Seuren and V. A. Zivkovic, Mixed-signal Design-for-Test: CTAG.AMS, Worldwide Technology Conference, Paris, France, 9-12 November 2005.

Q-Star

· H. Manhaeve, Current testing for nanotechnologies: a demystifying application perspective, IEEE European Test Symposium (ETS), May 2005.

· H. Manhaeve, Current testing for nanotechnologies: a demystifying application perspective, IEEE Asian Test Symposium (ATS), December 2005

ST

· Article in IEEE Computer magazine, july's issue: "An Open Platform for Developing Multiprocessos SoCs", M. Diaz Nava, P. Blouet, P. Teninge, M. Coppola, T. Ben-Ismail, S. Picchiottino, R. Wilson.

TIMA

· Bounceur, A. Dhayni, S. Mir and L. Rufer. Génération de vecteurs de test pour les MEMS non linéaires pour le calcul des noyaux de Volterra. In 8ème Journées Nationales du Réseau Doctoral de Microélectronique, Paris, France, May 2005, pp. 340-342.

· S. Mir, A. Dhayni, L. Rufer. Built-In Self-Test techniques for MEMS. In 1st International Workshop on Advances in Sensors and Interfaces (IWASI), Invited talk, Bari, Italy, 19-20 April 2005, pp. 34-38.

· A. Dhayni, S. Mir and L. Rufer. Evaluation of impulse response based BIST techniques for MEMS in the presence of weak nonlinearities. In 10th European Test Symposium, Tallin, Estonia, May 2005, pp. 82-87.

· A. Dhayni, S. Mir, L. Rufer and A. Bounceur. Autotest Intégré des Microsystèmes Nonlinéaires. In 8ème Journées Nationales du Réseau Doctoral de Microélectronique, Paris, France, May 2005, pp. 256-258.

· L. Rufer, A. Torres, S. Mir, M. O. Alam, T. Lalinsky, and Y. C. Chan, SAW chemical sensors based on AlGaN/GaN piezoelectric material system: acoustic design and packaging considerations. In 7th Int. Conf. on Electronics Materials and Packaging, EMAP 2005, Dec. 11-14, 2005, Tokyo Inst. of Technology, Japan.

· E. Simeu and S. Mir. Parameter identification based diagnosis in linear and nonlinear mixed-signal systems. 11th IEEE International Mixed-Signals Testing Workshop, Cannes, France, June 2005, pp. 140-147.

· E. Simeu, S. Mir and L. Rufer , Concurrent testing of embedded systems: adapting automatic control techniques to microelectronics, in 16th IFAC World Congress, Invited Talk, Prague, Czech Republic, July 2005.

TIMA & ST

· L. Rolíndez, S. Mir and G. Prenat. Digital test of a sigma-delta modulator in a mixed-signal BIST architecture. In SPIE Microtechnologies for the New Millennium, VLSI circuits and systems II, Sevilla, Spain, May 2005.

· G. Prenat, S. Mir, L. Rolíndez, and D. Vázquez, A low-cost digital frequency testing approach for mixed-signal devices using SD modulation. Microelectronics Journal. Elsevier, Vol. 36, 2005, pp. 1080-1090

· R. Kheriji, V. Danelon, J.L. Carbonero and S. Mir. Optimising test sets for RF components with defect-oriented approach. In Design and Test Conference in Europe, Munich, Germany, Vol. I, March 2005, pp. 170-171.

· R. Kheriji, V. Danelon, J.L. Carbonero, and S. Mir, Test orienté défaut pour les circuits radio fréquences. In 14ème Journées Nationales Microondes, Nantes, France, May 2005. |