We were deeply saddened to learn of the sudden death...

Read MoreThe Laboratoire d’Informatique, de Robotique et de Microélectronique de Montpellier (Laboratory of Computer Science, Robotics and Microelectronics of Montpellier) is a major multi-disciplinary French research center located in the South of France. It is affiliated with the University of Montpellier and the French National Center for Scientific Research (Centre National de la Recherche Scientifique, CNRS). It conducts research in Computer Science, Microelectronics and Robotics and is organized along 3 departments comprising 19 international research teams assisted by central services personnel… next

LIRMM researchers selected by NVIDIA as part of the Academic Grant Program

The research project “Dexterous Robotic Manipulation with Advanced Tactile Sensing,”...

Read MoreDeepPulseNeuro, winner of the i-Lab 2025 competition

The DeepPulseNeuro project was recognized at the 2025 edition of...

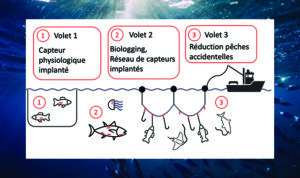

Read MoreThe ENTREMETS project honored by the CNRS MITI

The ENTREMETS project – Development of sensors and sensor networks...

Read MoreThe executive team