Équipe ADAC

ADAptive Computing

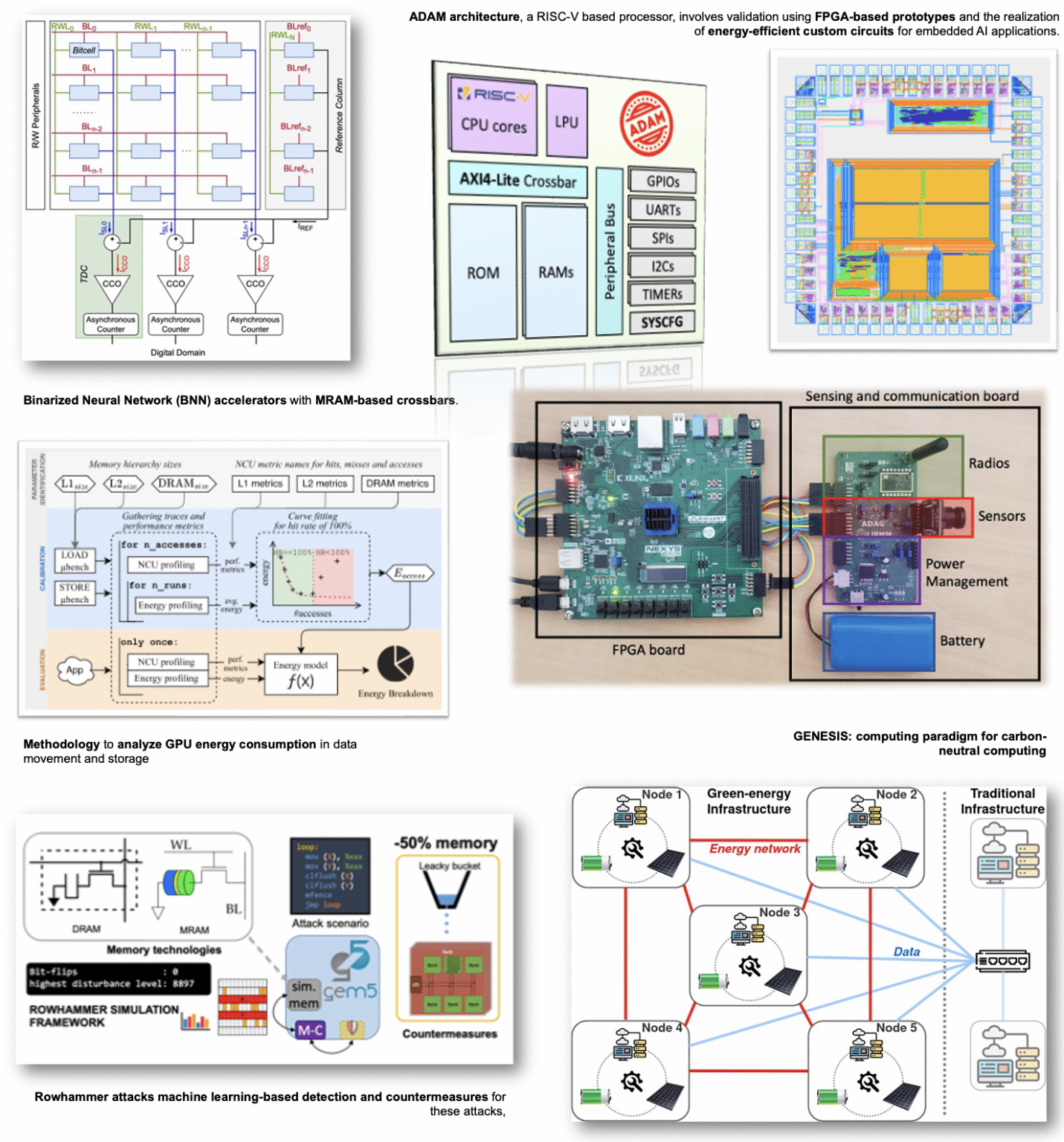

L’équipe ADAC (ADAptive Computing) du département microélectronique ambitionne de concevoir des architectures et systèmes de calcul à la fois intelligents, sécurisés, performants et éco‐responsables. Parmi les grandes questions scientifiques adressées, ADAC s’interroge sur l’optimisation de l’IA dans les architectures pour maximiser la performance tout en réduisant la consommation d’énergie, étudie notamment comment les nouvelles technologies peuvent contribuer à l’efficacité énergétique des systèmes de calcul, évalue les solutions architecturales pour protéger les systèmes contre les menaces émergentes, et vise à concevoir des systèmes capables de répondre aux exigences de soutenabilité et de réduction de l’empreinte carbone. L’équipe est impliquée dans les Programmes et Projets Exploratoires de Recherche (PEPR) en Intelligence Artificielle, Cybersécurité et Électronique. De plus, elle entretient des partenariats solides avec des acteurs européens de renom tels que l’IMEC et participe à des projets ambitieux tel que le projet GENESIS, qui se concentre sur la sobriété énergétique.

Permanents

Abdoulaye Gamatié, Directeur de recherche, CNRS

Florent Bruguier, Maître de conférences, UM

William Pensec, Maître de conférences, UM

Gilles Sassatelli, Directeur de recherche, CNRS

Lionel Torres, Professeur des universités, UM

Pascal Benoit, Professeur des universités, UM

David Novo, Directeur de recherche, CNRS

Michel Robert, Professeur des universités, UM

Doctorants

Mohammadali Zoroufchian, UM

Justin Chikhaoui, CNRS

Nassim Riadi, CNRS

Johann Teissier, UM

Felipe Paiva Alencar, UM

Enzo Rafinesque, UM

Soraya Mobaraki, CNRS

Clement Brichart, CEA

Bruno Lovison Franco, UM

Ali Ait Hassou, UM

Jean Nicaise Akaffou, INPHB

Gabriel Hautreux, CINES

Victor Cook, CNRS

Autres personnels

Ana Tacuri, CDD Ingénieur-Technicien, CNRS

Ismael Samaye, ATER, UM

Aymen Romdhane, Doctorant externe, CEA

Luis Bertran Alvarez, CDD Chercheur, CNRS

Collaborateurs réguliers :

Les recherches menées par l’équipe s’inscrivent dans un des trois axes suivants, chaque permanent étant en général impliqué sur 2 axes (un axe principal et un axe secondaire).

Axe 1. Architecture et outils pour l’accélération matérielle

Les recherches menées dans cet axe visent à repousser les limites du calcul haute performance (HPC), de l’intelligence artificielle (IA) et de l’edge computing. Elles s’articulent autour de l’optimisation des interconnexions, de la spécialisation des unités de calcul et de l’intégration de technologies mémoire émergentes.

Les travaux sur les réseaux sur puce (NoC) s’appuient sur des méthodes d’apprentissage automatique pour améliorer les transactions entre unités de traitement tout en préservant la flexibilité d’usage. L’amélioration des outils de simulation passe par l’extension de simulateurs open-source (gem5) et la mise en place de méthodologies de calibration basées sur des microbenchmarks. Une approche par accélération FPGA permet de contourner les limites des simulations classiques, avec des interfaces simplifiées ne nécessitant pas d’expertise RTL (projet ANR F3CAS, collaboration avec ETHZ).

La spécialisation des unités de calcul est abordée à travers l’analyse des performances et de la consommation énergétique des tâches IA sur GPU. Une architecture combinant processeur RISC-V et accélérateurs dédiés est proposée pour concilier flexibilité algorithmique et efficacité matérielle.

L’intégration de mémoires émergentes, telles que les MRAM, fait l’objet d’une co-optimisation architecture-technologie. Une collaboration avec l’IMEC explore la conception de mémoires cache SRAM sur puce en technologie 3D monolithique.

Axe 2. Sécurité, fiabilité et résilience : vers des systèmes informatiques dignes de confiance

Les recherches menées dans ce thème visent à renforcer la sécurité des systèmes embarqués dans des environnements contraints, en particulier dans le contexte de l’Edge Computing. Les travaux portent sur la protection des processeurs et des mémoires face aux attaques matérielles et logicielles, ainsi que sur la résilience des architectures.

Des solutions de cryptographie légère ont été évaluées, et des vulnérabilités ont été identifiées sur des cryptoprocesseurs post-quantiques via des analyses électromagnétiques. La sécurité des mémoires est abordée par la détection d’attaques telles que ROP et Rowhammer, avec des contre-mesures basées sur l’apprentissage automatique.

Dans le domaine de l’Edge Computing, un protocole sécurisé inspiré de la Blockchain, Wallance, a été développé, offrant des performances optimisées en termes de mémoire, latence et consommation. Des contributions ont également été apportées à la fiabilisation des micro-réseaux DC reconfigurables pour l’intégration des énergies renouvelables.

La robustesse des technologies mémoire émergentes, notamment les MRAM, est explorée à travers des structures innovantes pour la génération de nombres aléatoires et de fonctions non clonables (PUF), ainsi que l’étude de leur comportement face aux radiations et aux attaques.

Axe 3. Vers des systèmes informatiques éco‐responsables, du circuit aux infrastructures à grande échelle

Les recherches de cet axe visent à réduire l’impact énergétique des systèmes informatiques, en réponse à la consommation croissante liée à l’IA, notamment les modèles génératifs. L’équipe explore des solutions frugales, de l’optimisation des architectures jusqu’aux infrastructures.

Des travaux sont menés sur les nœuds IoT avec intégration de MRAM dans des architectures intermittentes, évaluées via des plateformes de prototypage. Des architectures basées sur ARM et RISC-V ont été développées pour optimiser la mémoire selon les besoins applicatifs. Des gains énergétiques significatifs ont été démontrés.

L’introduction d’accélérateurs BNN et de calcul en mémoire est étudiée dans le cadre de projets PEPR. Une unité MAC flexible a été conçue pour microcontrôleurs, avec des améliorations en énergie et surface. Des GAN sont utilisés pour générer des topologies optimisées de NoC.

Le projet GENESIS propose des centres de données à faible impact, avec gestion dynamique de l’énergie verte. Un prototype a été déployé à Polytech Montpellier, avec des résultats prometteurs. Le volet sociétal explore l’acceptabilité et l’impact environnemental, en collaboration avec des chercheurs en urbanisme.

Le projet Emergences du PEPR IA explore des modèles d’IA physiques comme les EBM, avec développement de circuits analogiques capables d’apprentissage embarqué. Une puce de test est prévue pour 2025, avec des perspectives vers l’apprentissage incrémental autonome.

PEPR Electronique

- Projet EMCOM : L’électronique pour le calcul

- Projet CHOOSE : Action concertée transverse (Design)

PEPR IA

- PRC

- ANR – AAPG2024 – CE39 – Sécurité globale, résilience et gestion de crise, cybersécurité

- PRC

- ANR – AAPG2023 – CE39 – Sécurité globale, résilience et gestion de crise, cybersécurité

IMEC Contract

Heterogeneous memory systems with emerging non-volatile technologies

Contrat AXIAUM

Contrat EXPLAINER

- IMEC, Interuniversity Microelectronics Centre, Belgium

- Brême University, Germany

- ETH Zurich, Swiss Federal Institute of Technology in Zurich, Suisse

- Université Osaka

- KIT

Titre : Apprentissage avec modèles basés sur l’énergie pour le calcul à l’edge

Doctorant : Mohamed Watfa

Date de soutenance : 2025-12-17

Directeur de thèse :

Gilles Sassatelli

Titre : Méthodes de Logic-Locking résistantes aux attaques par canaux cachés

Doctorant : Nassim Riadi

Date de soutenance : 2025-12-09

Directeurs de thèse :

Pascal Benoit,

Florent Bruguier

Titre : Modélisation et évaluation d’un concept de mini data center à faible impact environnemental

Doctorant : Ismael Samaye

Date de soutenance : 2025-11-12

Directeurs de thèse :

Abdoulaye Gamatié,

Gilles Sassatelli

Titre : Analyse et Modélisation de Réseaux d’Interconnexion Cohérent Puce-à-Puce

Doctorant : Luis Bertran Alvarez

Date de soutenance : 2025-03-27

Directeurs de thèse :

Pascal Benoit,

David Novo

Titre : Etude de la résistance aux attaques par canaux auxiliaires dimplémentations de primitives cryptographiques basées sur les réseaux euclidiens pour la cryptographie post-quantique

Doctorant : Rafael Carrera Rodriguez

Date de soutenance : 2024-11-25

Directeur de thèse :

Pascal Benoit

Titre : Techniques Avancées D’analyse De Performance Pour Évaluer L’efficacité Des Accélérateurs Graphiques Pour Les Applications D’apprentissage Automatique

Doctorant : Paul Delestrac

Date de soutenance : 2024-09-17

Directeurs de thèse :

David Novo,

Lionel Torres

Titre : Développement et évaluation de solutions de protections des DRAM et MRAM contre l’attaque Rowhammer

Doctorant : Loic France

Date de soutenance : 2022-12-16

Directeur de thèse :

Pascal Benoit

Titre : Exploration des architectures de mémoire des microcontrôleurs pour le calcul intermittent embarqué

Doctorant : Theo Soriano

Date de soutenance : 2022-12-15

Directeur de thèse :

Pascal Benoit

Titre : Simulation précise du mouvement des données au sein des systèmes mobiles multicurs modernes

Doctorant : Quentin Huppert

Date de soutenance : 2022-12-06

Directeur de thèse :

Lionel Torres

Titre : Étude d’architectures dédiées aux systèmes embarqués intelligents et efficaces en énergie

Doctorant : Guillaume Devic

Date de soutenance : 2021-12-03

Directeurs de thèse :

Abdoulaye Gamatié,

Gilles Sassatelli

Titre : Exploration des solutions de reconfiguration dynamique pour améliorer la fiabilité des micro-réseaux à courant continu

Doctorant : Francesco Di Gregorio

Date de soutenance : 2021-11-19

Directeurs de thèse :

Gilles Sassatelli,

Abdoulaye Gamatié

Titre : Techniques dapprentissage pour le contrôle adaptatif multi-niveaux du calcul distribué

Doctorant : Maxime Mirka

Date de soutenance : 2021-11-12

Directeurs de thèse :

Gilles Sassatelli,

Abdoulaye Gamatié

Titre : Effets des radiations de lenvironnement spatial sur les mémoires spintroniques

Doctorant : Odilia Coi

Date de soutenance : 2021-10-14

Directeur de thèse :

Lionel Torres

Titre : Étude et conception de méthodes de protection face aux attaques par corruption de mémoire pour systèmes embarqués dans le contexte de l’Internet des Objets.

Doctorant : Yohan Boyer

Date de soutenance : 2020-12-17

Directeur de thèse :

Pascal Benoit

Titre : De la vulnérabilité des nuds capteur à la certification des transactions sur le réseau, une approche de la sécurisation de lInternet des Objets.

Doctorant : Loïc Dalmasso

Date de soutenance : 2020-12-15

Directeur de thèse :

Pascal Benoit

Titre : Primitives de sécurité à base de mémoires magnétiques

Doctorant : Frederic Ouattara

Date de soutenance : 2020-11-06

Directeur de thèse :

Lionel Torres

Titre : Systèmes intégrés adaptatifs ultra basse consommation pour lInternet des Objets

Doctorant : Guillaume Patrigeon

Date de soutenance : 2020-07-16

Directeur de thèse :

Pascal Benoit

Titre : Étude et conception de mécanismes de rupture et de filtrage de protocoles industriels

Doctorant : Peter Rouget

Date de soutenance : 2019-08-29

Directeurs de thèse :

Pascal Benoit,

Lionel Torres

Titre : Intégration de technologies de mémoires non volatiles émergentes dans la hiérarchie de caches pour améliorer l’efficacité énergétique

Doctorant : Pierre-Yves Péneau

Date de soutenance : 2018-10-31

Directeurs de thèse :

Abdoulaye Gamatié,

Gilles Sassatelli

Titre : Investigation des techniques de surveillance pour les systèmes intégrés auto-adaptatifs

Doctorant : Mohamad El Ahmad

Date de soutenance : 2018-10-18

Directeurs de thèse :

Pascal Benoit,

Gilles Sassatelli

Titre : Exploration de systèmes multicoeurs basés sur des réseaux de communication intégrés sur silicium

Doctorant : Charles Effiong

Date de soutenance : 2017-11-16

Directeurs de thèse :

Gilles Sassatelli,

Abdoulaye Gamatié

Titre : Réseau sur puce sécurisé pour applications cryptographiques sur FPGA

Doctorant : Rémy Druyer

Date de soutenance : 2017-10-26

Directeurs de thèse :

Lionel Torres,

Pascal Benoit

Titre : Conception de Circuit Intégré Innovant GALS (Globally Asynchronous Locally Synchronous) Non-Volatile pour Application Spatiale

Doctorant : Jeremy Lopes

Date de soutenance : 2017-09-18

Directeur de thèse :

Lionel Torres

Titre : Hardware and Software Prototyping of a Miniature Star Tracker System for a Nano-Satellite

Doctorant : Andrey Khorev

Date de soutenance : 2016-12-13

Directeur de thèse :

Lionel Torres